数カ月ごとに新しい電子機器が発表され、それらは通常、新世代の高性能な半導体によって、小型化され、よりスマートで高速、そして、より広い帯域幅や、より高い電力効率へと改良されています。

新しい電子機器が次々と登場することが当たり前と思うようになった私たちのデジタル社会ですが、その裏では、電子機器に必要な次世代半導体のために、技術者たちが半導体の開発ロードマップに真剣に取り組んでいるのです。

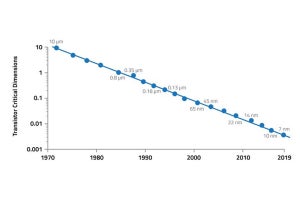

長い間、半導体の進歩は、トランジスタのサイズを縮小し、ウェハ上にさらに多くのトランジスタを形成できるようにすることで達成され、これによってトランジスタの数は12~24カ月ごとに倍増してきました。これは「ムーアの法則」として知られています。この間、ムーアの法則のペースを維持するために、銅/低誘電率相互接続、トランジスタ新材料、マルチパターニング方式、3次元(3D)アーキテクチャなど、大幅な技術革新が必要とされてきました。

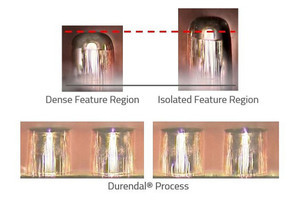

3D構造の開発への移行は新たな課題をもたらし、その課題はアスペクト比の増加とともに深刻化しています。ご想像の通り、3Dではデバイスの設計方法を根本的に変える必要があり、そのためには新しい材料と新しい成膜およびエッチング手法が必要になります。本稿では、半導体産業が3次元化に向けて、乗り越えてきた重要なマイルストーンを紹介します。

準備期:平面処理

集積回路の製造は、平らなシリコンシートを用意し、その表面にさまざまな構造体を配置し、それらを配線でつなぐという2次元(2D)の課題から始まりました。その製造工程は、材料の層に成膜し、フォトリソグラフィを用いてパターニングし、露出した部分にエッチングを施して必要な機能を作り上げることで完了します。これは、エレクトロニクス産業にとって大きなブレークスルーでした。

技術的要件が進展するにつれ、より小さな構造を維持するために、より多くの回路をより狭いスペースに構築する必要が出てきました。かつては比較的簡単だった工程が、次第に複雑になっていったのです。

2D構造の製造コストが増え続け、2D平面でのスケーリングするための実現可能なアプローチが出尽くしたため、3D構造がより注目されるようになりました。半導体業界では、10年以上前に3Dに対応した初期の選択エッチングアプリケーションの開発に着手し、パッケージングから不揮発性メモリ、さらにはトランジスタ自体に至るまで、その範囲を拡大し続けてきました。

トランジスタが3Dに移行

多くの電子システムに貢献しているのがトランジスタです。従来、トランジスタは平面構造で、その特性はトランジスタ・チャネルの幅や長さで決まっていました。トランジスタの動作制御は、チャネルにかぶせて配置されたゲートによって行います。しかし、この方法では、チャネルの他の側面や底面は制御できないため、ほんの限られた制御がなされるだけでした。

平面からの最初の移行は、フィンを設けてチャネル3面でゲートによる制御を可能にしたことで実現しました。しかし、最適に制御するにはトランジスタの4面すべてにアクセスする必要があるため、現在ではゲート・オール・アラウンド(GAA)トランジスタへの移行が進んでいます。GAA構造では、複数の配線またはシートが互いに重なり合い、ゲート材料がチャネルを完全に取り囲んでいます。