2021年4月12日より開催されているGTC 21の基調講演の中でNVIDIAの創立者兼CEOのJensen Huang氏は、データセンタ向けの高性能Arm CPUを発表した。AI処理の性能は従来のCPUに比較して10倍になると発表され、NVIDIAの株価は5%あまり値上がりし、Intelの株価は4%あまり値下がりした。

-

図1 高メモリバンド幅のデータセンタCPU「Project Grace」を発表するNVIDIAの創立者兼CEOのJensen Huang氏 (出典:このレポートのすべての図は、Huang CEOの基調講演の発表スライドをキャプチャしたものである

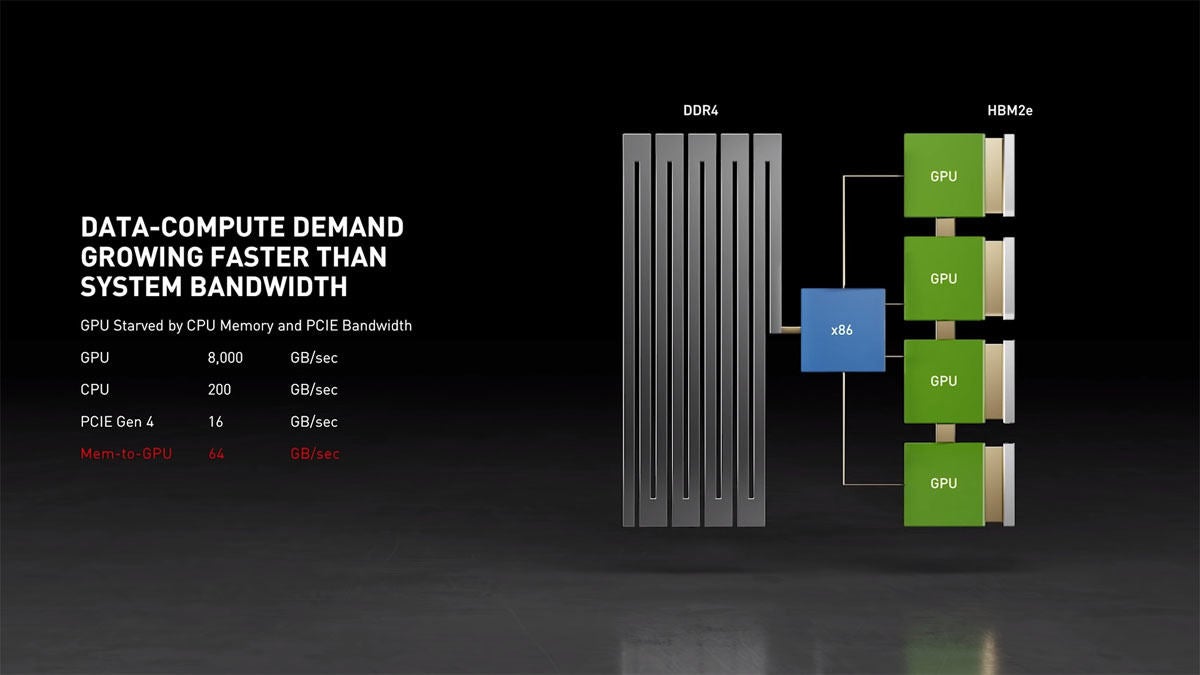

NVIDIAはNV-Linkを開発し、GPU同士を高速のネットワークで接続できるようにしたが、大容量のDDR3/4メモリにアクセスするにはCPUを経由する必要があり、この部分がネックとなり、メモリからGPUへのデータ供給速度はあまり速くなっておらず、十分な性能向上は実現されていなかった。

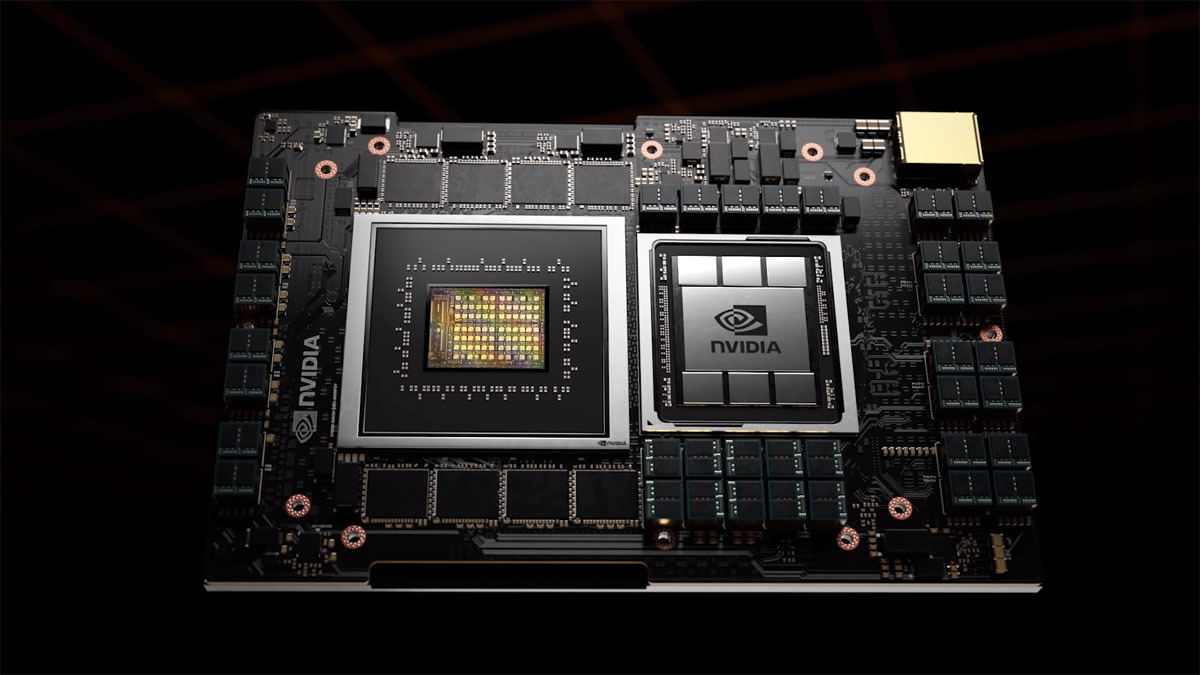

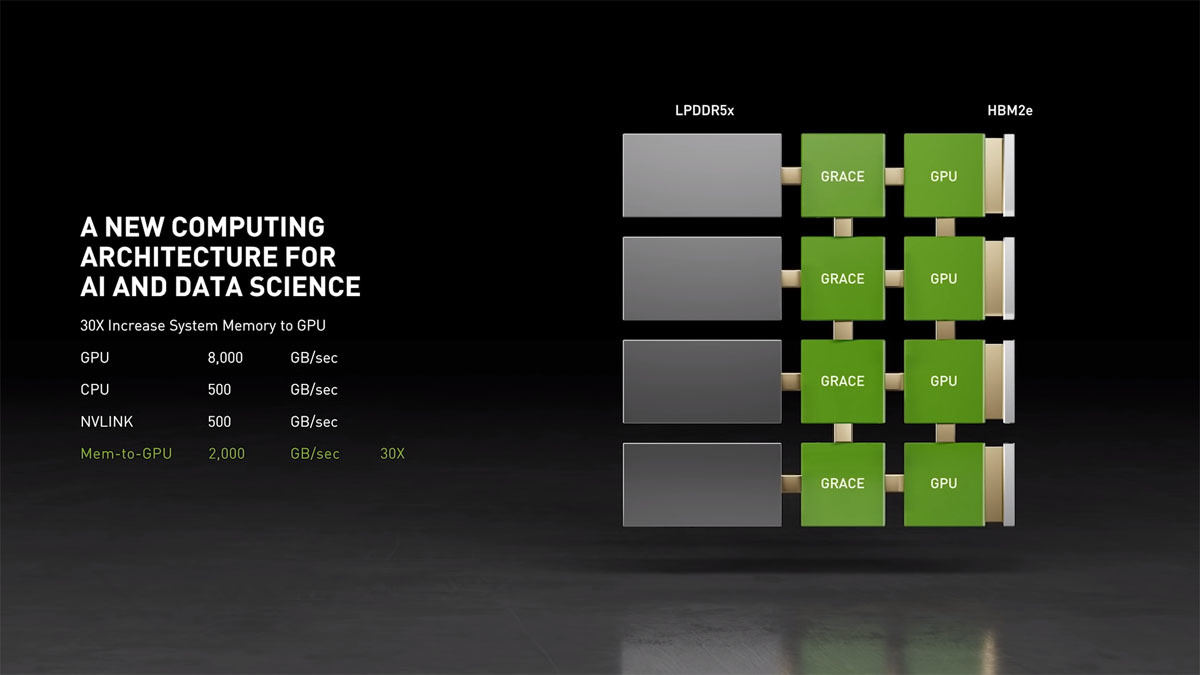

そこでNVIDIAはNV-Linkをサポートして、GPUと高速のデータ伝送ができ、加えて、高バンド幅のLPDDR5xメモリが接続できるCPU「Grace」を開発した。この写真ではLPDDRメモリが8個搭載されているようである。プリント板の専有面積ではA100 GPUよりもGrace CPUの方が大きく、メモリの接続ピン数が多いことがうかがわれる。

なお、Graceという名称は、初期の女性プログラマでCOBOLを開発するなどの功績をあげたGrace Hopper氏にちなんでつけられたものである。付け加えると、Grace Hopper氏はコンピュータ科学者として海軍に勤め、准将にまで昇進した。

次の図3の上側の図のように、GPUは直結されたHBM2eメモリと、CPUを経由してアクセスするDDR4メモリで作られたメインメモリ(CPUメモリ)を使う。この構成ではCPUメモリの容量はGPUメモリの3倍であるが、データの移動速度であるバンド幅はGPUメモリの1/40程度しかない。これがGPUの計算処理速度を制限してしまう。

一方、4個のGrace CPUを使った場合はメインメモリとGPUの間のバンド幅は2000GB/sとなり、上側の図の構成と比較するとメモリバンド幅は30倍程度になる。大規模なAI処理では、GPUメモリでは容量不足で、かつ、メモリへのアクセス回数が多く、このバンド幅が性能ネックになることがある。そのようなケースは図3の下側の図のようにGrace CPUを使えば、10倍の性能が得られる。また、整数演算性能の指標であるSPECintベンチマークでは、今日のDGXは450 SPECint_rate程度の性能であるが、4個のGrace CPUを使えば、2400 SPECint_rateの性能が得られるという。しかし、HBM2eメモリに全部のデータが入ってしまうケースでは、図3の上下の構成でメモリバンド幅は同じで、性能差はほとんど出ないと考えられる。

図3 上は従来のCPUを使った場合、下はGrace CPUを使った場合。GPUとHBM2eの間のバンド幅は8000GB/sであるが、通常のCPUとDDR4メモリの間のバンド幅は200GB/sしかない。一方、Grace CPUの場合はメモリとの間のバンド幅は500GB/sで、通常のCPUの場合と比較してLPDDR5xメモリとのバンド幅は30倍に向上している

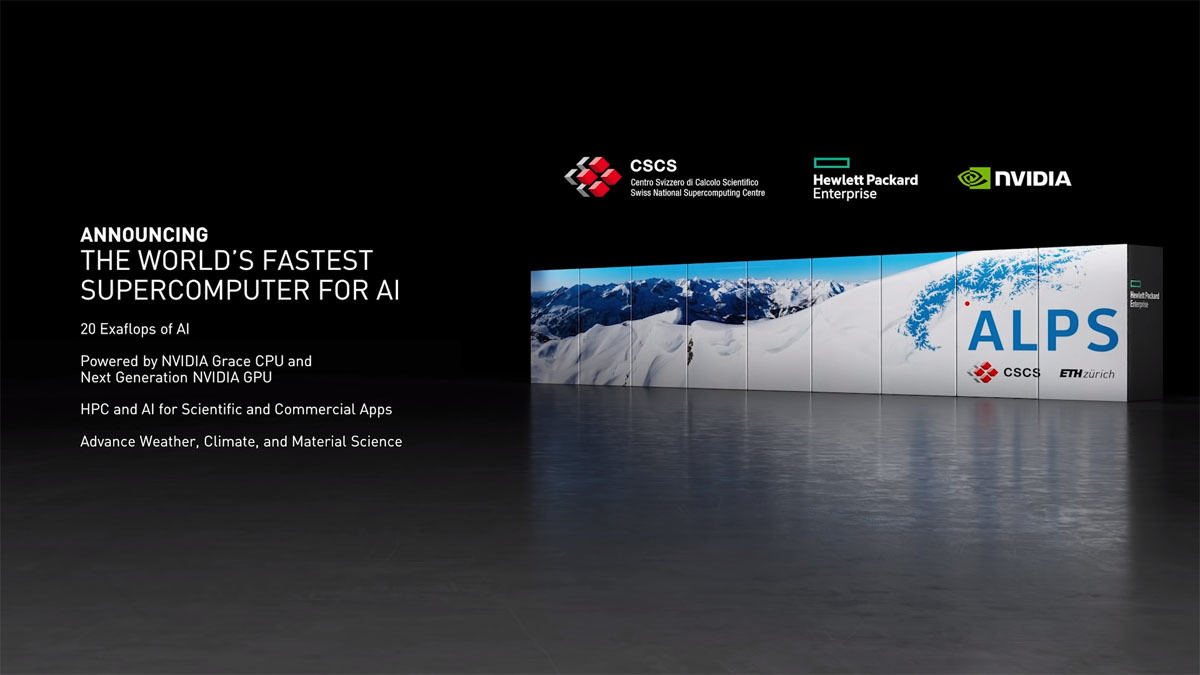

スイスの国立スパコンセンターであるCSCSと米国のロスアラモス国立研究所が、Grace CPUを使うスパコンを導入することを発表した。CSCSは2016年のTop500でヨーロッパ1位を獲得し、2019年11月までその地位を保ったPiz Daintを持つヨーロッパ屈指のスパコンセンタである。そして、このPiz Daintの後継となるのがAlpsである。Alpsは2023年に稼働の予定で、AI性能では2.8ExaFlopsのNVIDIAのSeleneスパコンの7倍の性能と発表されている。したがって、AI性能では20ExaFlops程度の性能になると考えられる。

ロスアラモス国立研究所の方は、2023年という時期は発表されたが、スパコンの規模や名称などは発表されていない。