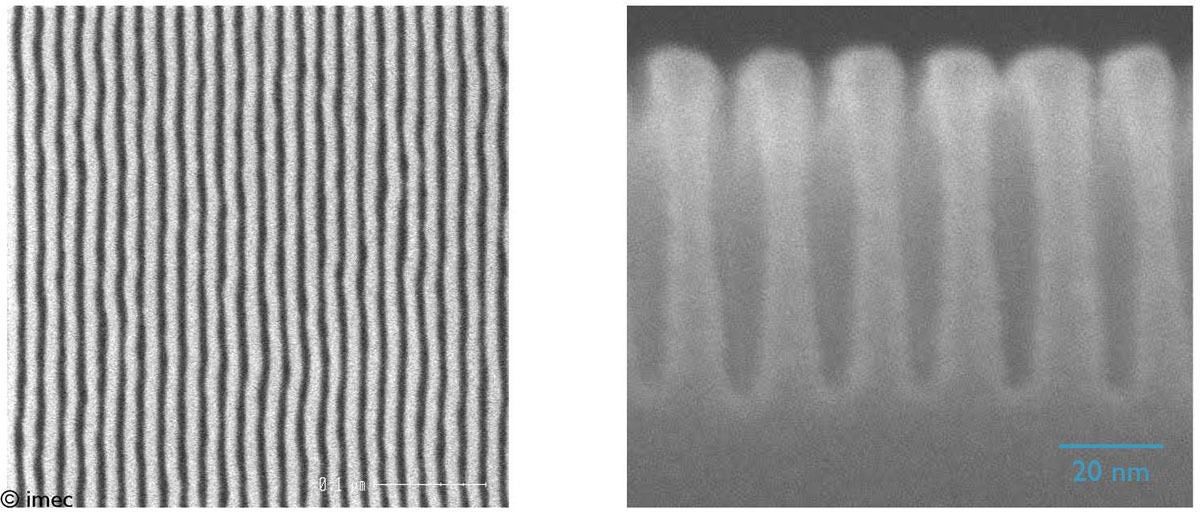

ベルギーの独立系半導体研究機関imecは、東京エレクトロンや日産化学、東京応化工業といった日本の装置・素材メーカーなどと協業して、ブロック共重合体(block copolymer:BCP)ベースのプロセスを使用して、18nmピッチでライン/スペース(L/S)をパターニングする誘導自己組織化(directed self-assembly:DSA)の有効性を実証したことを発表した。

最適化されたドライエッチングケミストリーを使用して、パターンの下にある厚いSiN層に正常に転写できたとのことで、これにより、さらに詳しいパターン欠陥検査が可能になったとするほか、今回の成果について、将来のサブ2nmテクノロジーノードでの量産に向けて、従来のEUVリソグラフィを用いたパターニングを補完するDSAの可能性を裏付けることができたともしている。

今回の研究成果の詳細については、2月下旬に開催されたリソグラフィの国際会議である「SPIE Advanced Lithography Conference」で発表された。

半導体デバイスのさらなる微細化を実現するためには、20nm未満のピッチを持つ形状のパターニングが必要になるが、従来のトップダウンリソグラフィのパターニングでは、感光性材料と光との反応による固有の問題(確率的な焼き付け不良や線端/線幅の粗さ(LER/LWR)など)がこれまで以上の課題としてのしかかってくる。そのため半導体業界は2010年以降、フォトリソグラフィベースのパターニングを補完、ならびにさらに拡張するための潜在的な手法として、誘導自己組織化(Directed Self-Assembly:DSA)などのボトムアップパターニング手法の研究を本格的に進め始めた。

DSAは、ブロック共重合体(BCP)のミクロ相分離を使用してパターンを定義する。パターンは、ポリマーの組成とサイズを調整することで設計できる。アセンブリは、ライン/スペースまたは穴のいずれかのプレパターンを使用して行える。これにより、ガイドテンプレートよりもはるかにタイトなピッチ(30〜5nm)の規則的なパターンを得ることができるようになるという。すでにimecでは2019年に、PS-b-PMMAブロック共重合体のDSAを活用することで、低欠陥率の安定した28nmピッチのライン/スペースのパターンを生成できることを報告している。

今回の研究はそれらの成果を基に、第2世代のブロック共重合体、つまりimecのDSA材料パートナー(独Merck、米Brewer Science、日産化学、東京応化工業)のhigh-χ(chi) BCPを活用する形で、DSAプロセスをサブ20nmピッチパターニングで実現することを目指して進められたという。

imecのDSA研究者であるHyo Seon Suh氏は、「ブロック共重合体は2つの異なったブロックを含んでおり、Χ(ギリシャ文字のchi)はブロック間のポリマーの相互作用の程度を示すパラメータで、似通った共重合体の場合は、Xの値は小さく、大きく異なっている場合はXの値は大きくなる。研究の第一段階ではXの比較的小さい、混合しやすい共重合体を用いたが、第2段階ではXの大きな、相転移の起きやすい共重合体を用いて、20nm未満の微細パターンの形成を目指した」とhigh-X材を使用した理由を説明している。

今回形成されたパターンは、193nmの液浸ArFリソグラフィを用いて成形された90nmフルピッチガイドパターンをもとにして、HVM互換トラック(SCREEN Semiconductor Solutions)を用いてhigh-χ BCPの60秒間の自己組織化を実施。ベストケースでは、無転位の18nmピッチのライン/スペースパターンが得られたという。

さらに、東京エレクトロンとの緊密な協力によって開発されたドライエッチングケミストリーにより、18nmのライン/スペースパターンを、顕著なライン揺れやライン崩壊なしに、欠陥検査を追跡するのに十分な深さのSiN層に正常に転写することができたという。

なおimecでは、次の研究段階として、このパターン化された層を使用して、欠陥検査とLER/LWR測定用の計測を行う予定としている。