オーストリアに本拠を置く半導体製造装置メーカーであるEV Group(EVG)は、先端パッケージング向けに新しいマスクレス露光技術(MLE:Maskless Exposure)を開発し、近く発売を予定しているリソグラフィ装置に搭載すると発表した。ラインアンドスペースの解像度は2μm以下としている。半導体バックエンド(パッケージング)のほか、MEMS、バイオメディカルおよび高密度プリント回路基板(PCB)などのアプリケーションも想定している。

新たな課題に直面するバックエンドリソグラフィ

ヘテロジニアスな素子集積が半導体の技術革新を牽引し、先端パッケージング、MEMSおよびPCB(プリント基板)市場に影響を与えるようになるにつれて、バックエンドリソグラフィに対する要求は従来以上に厳しくなってきている。

たとえば先端パッケージングでは、再配線層(RDL)やインターポーザーの密集ライン/スペース(L/S)が続く部分において、最小解像度に対する要求がますます厳しくなっている。場合によって 2μmあるいはそれ以下の解像度が求められる一方、パターニングにはダイ配置のばらつきや費用対効果の高い樹脂基板の使用にも対応できる、より高い柔軟性も要求されている。

また、さらに高度なオーバーレイ精度や、垂直側壁へのパターニングに対するより深い焦点深度への要求も高まっている。ファンアウトウェハレベルパッケージング(FoWLP)において、ウェハの歪みに起因するパターンの歪みやダイシフトの最小化、厚膜および薄膜レジストへの対応といった新たな要件がパッケージングリソグラフィ装置に求められている。EMS製造では、その複雑な製品構成により、マスク/レチクルにかかる間接費が所有コスト(CoO)に大きな影響を及ぼす一方、トレンチ内へのパターニングに際し優れた焦点制御は不可欠である。PCBおよびバイオメディカル分野では、幅広い加工寸法および基板サイズに対応するため、高度なパターン柔軟性に対する需要が高まっている。

すべてのレジストとウェハサイズに対応できるMLE 技術

バックエンドリソグラフィ向けの露光装置としては、たとえば、伝統的なプロキシミティ・マスクアライナ(g、h、iライン対応、ラインアンドスペース解像度>3μm)やBEOLプロジェクションアライナ(iライン対応、解像度>1.5μm)が普及しているが、いずれもマスクやレティクルが必要である(図1)。マスクレスとしては、レーザーダイレクトイメージングがあり、解像度は高くできるものの、スループットが著しく低い。そこで、EVGとしては新たな手法を採用することにしたという。

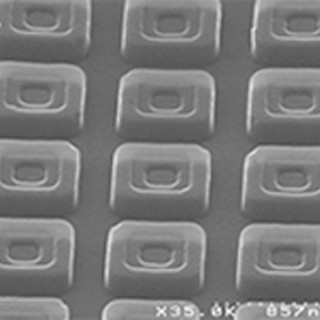

今回開発したMLE技術は、クラスター化された多数の書き込みヘッドと多波長高出力UV光源を適切に組み合わせて構築したマルチヘッドでスキャンすることで、すべての市販のレジストを使用することができ、かつすべてのサイズのウェハやパネルに対応可能としている(図2)。

これにより、バックエンドリソグラフィの次世代要求を満たしつつ、これまでフォトマスクの維持・管理などに必要だった間接費を削減できるとするほか、基板表面全体への高解像度(<2μm L/S)およびつなぎ目の無いマスクレス露光を高スループットと低コストオブオーナーシップ(CoO)で可能にするともしている。

また要求に応じてUV露光ヘッドを追加したり取り外すことにより、装置構成を調整することができ、これにより研究開発から量産体制への迅速な移行、スループットの最適化、さまざまな基板サイズや材料への適応を可能にするとともに、小型のシリコン/化合物半導体ウェハからパネルサイズまで、あらゆる基板を処理できるようになるとする。さらに柔軟で拡張性の高い高出力UVレーザー光源は多波長露光をオプションで備えているため、フォトレジストの種類に依存しないパターニング性能を達成できるとしている。

-

図3 異なるレジストを用いたパターニング例。(上)MLE技術による高解像度AZ MIR 701 ポジレジストのパターニング例、(下) MLE技術を用いたJSR THB 151N ネガレジスト(50μm厚)パターニング例 (出所:EVG)

なお、EVGでエグゼクティブ・テクノロジー・ディレクターを務めるPaul Lindner氏は「MLEはEVGの既存リソグラフィ装置を補完するとともに、従来のリソグラフィ方式が拡張性やCoOなどの制約により適用が難しくなることを想定し、こうした場面で新たに活用し得るように開発・設計した。この新しいMLE技術は、ステッパーなど、他のパターニング技術では性能やコストの面で妥協せざるを得ないバックエンドリソグラフィのアプリケーションにおいて、優れた性能を発揮するだろう」と述べている。