PCI/PCI Express(PCIe)の仕様を策定しているPCI-SIGは米国時間の6月18日からサンタクララで「PCI-SIG Developer Conference 2019」を開催しているが、その初日に行われた記者説明会において、PCIe Gen5のSpecificationの完成ならびに、PCIe Gen6について言及があった。

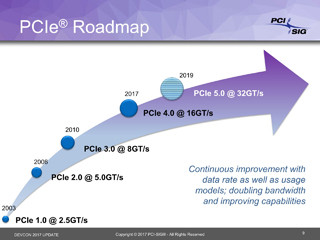

普及が遅れているPCIe Gen4(Photo01)であるが、すでにOffial FYI(For Your Information)Testが2018年12月に行われており、2019年第3四半期には公式にCompliance Testの仕様もまとまる予定である。こちらに関してはすでに数社が対応製品を出荷済であり、ES(エンジニアサンプル)品まで含めるとかなりの数のメーカーが対応製品を出荷開始している状況なので、それほど問題では無いだろう。

-

Photo01:冷静に考えると"FYI"と"Official"は両立しないはずなのだが、それが両立してしまうというのは、要するに製品投入が遅れていて公式テストは出来ないけれど、ただ何かしらPCI-SIGがリードしてFYI Testを行わないといけない時期に来ているため、というあたりであろう

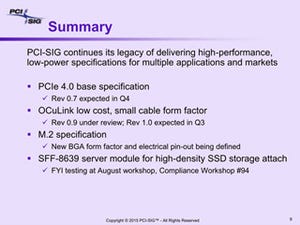

これに続いて今回仕様策定の完了が発表されたのがPCIe Gen5(Photo02)である。dB lossは4.0から8dB増えて36dBに達しており、色々厳しい気がする。ちなみにChannel Reachがどのくらいまで減ったかを確認したところ、一応ターゲットはコンシューマ向けには12inch、Backplaneでは36inchという答えがAl Yanes氏(Chairman, PCI-SIG)から返ってきたが色々条件があるようで、この辺りはSpecificationが確認でき次第またご紹介したいと思う。ちなみに今年中にPLDAが最初のIPをTape out予定だそうで、Synopsys/Cadenceなどもこれに続く形でIPを提供し始める事になると思われる。

-

Photo02:速度向上にあわせてSignal Integrityの改善などが施されたのはともかく、PCIe Gen4の時の様にImplementationに変更あるいは改良が施されたかどうかは現状不明

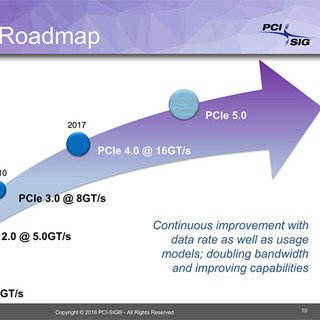

さて、これに続くのがPCIe Gen6である。トレンドとしては3年ごとに帯域が倍増しており、これにあわせる形で引き続き高速化していく、としている(Photo03)。

一般に仕様策定から搭載製品の出荷まで1~2年ほど(以前は1年掛からなかったが、最近は2年近くを要している)かかっている事を考慮すれば、今のところほぼ要求のトレンドに合致する形で仕様策定が行われているとは言えるだろう。

そのPCIe Gen6であるが、遂にBinary Signalingを捨てPAM4(4値パルス振幅変調)を採用することを明らかにした(Photo04)。背景にあるのは、特に100G以上のEthernetがPAM4を利用する関係でPAM4の技術が非常に標準的になっており、PCI Expressに採用するのが難しくなくなった、というあたりであろう。当然FECなどは色々考慮する必要はあるだろうが、技術的には道筋が立った形になる。

-

Photo04:冷静に考えれば、64GT/sの信号を銅線で流すのは無理ではないにしても非常に困難(特にPCI Expressはプロプラエタリなソリューションでなく、標準技術でこれを実現しないといけない)な事を考えれば妥当な選択だと思われる

このPAM4を採用したPCIe Gen6は2021年の標準化を目指している。可能性的に言えば、その後でPAM16を搭載したPCIe Gen7とかもありそうな展開になってきた感じである。まだまだPCIeの進化は止まりそうにない。