ベルギ―の独立系ナノテク研究機関imecは5月23日(ベルギー時間)、ベルギーのアントワープで開催されている「imec Technology Forum 2018」において、Unisantis Electronics Singaporeと共同研究による0.0184~0.0205μm2という小型SRAMセルに関する研究成果を報告すると発表した。

フラッシュメモリの発明者として知られる舛岡富士夫氏がCTOを務めることで知られるUnisantisは、縦型ゲート・オール・アラウンド(GAA)トランジスタの一種である、独自のSurrounding Gate Transistor(SGT)を開発し、DRAM、NAND、SRAMの共通シリコンプラットフォームとして活用することを目指しているベンチャー企業である。

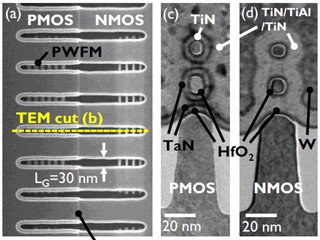

imecは、UnisantisとSGTを用いた 6T-SRAMの専有面積縮小の共同研究を行い、従来の平面に配置しているFETに比べて、垂直に配置されたシリコン柱のまわりを囲む構造によりSRAM面積を20~30%縮小させつつも、動作電圧、スタンバイリーク、動作安定性の点で従来構造のSRAMを超える性能を実現できることを確認したという。

SGTの概念を考案した舛岡氏は「SGTは、縦型GAAトランジスタの利点をすべて持ち合わせており、トランジスタをほぼ完ぺきに静電制御できる。SGTは、縦型ピラーがチャンネルを構成しているので、横型ナノワイヤ・トランジスタに比べて、専有面積を縮小する潜在性を秘めている」と述べている。

なお、imecとUnisantsisの技術者たちは、設計とプロセス技術を同時に最適化する手法を用いることで、ピラーピッチを50nmまで縮小し、これまでに公表されているSRAM面積よりも24%縮小することに成功したとしている。プロセス面では、N5(5nm)プロセスとの整合性を持たせており、1回露光EUVリソグラフィを採用することで、多重露光によるプロセス増加を回避し、製造コストを従来のFinFETベースのSRAM並みの抑えられるとしている。