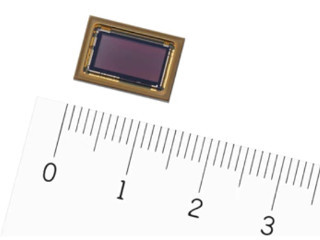

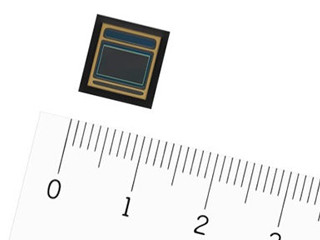

ソニーは2月13日、新たに開発したA/D変換器(ADC)を画素ごとに配置し、全画素同時に露光したアナログ信号を各々即座にデジタル変換(画素並列A/D変換)することで、グローバルシャッター機能を実現した、有効画素数146万画素の裏面照射型CMOSイメージセンサを開発したと発表した。

従来のカラムA/D変換方式のCMOSイメージセンサは、画素で光電変換したアナログ信号を行ごとにA/D変換して読み出すため、行ごとの読み出し時間のずれによる画像の歪み(フォーカルプレーン歪み)が発生していた。

今回、同社はサブスレッショルド領域で動作する小型の14ビットADCを開発。従来のカラムA/D変換方式に比べ、役1000倍のADCを搭載しても、低消費電力動作を可能とした。また、全画素同時に露光したアナログ信号を並列にデジタル変換することを可能とする方法として、約300万個のイメージセンサ部とロジック回路部の積層をCuのパッド同士で接続する「Cu-Cu接続」技術を開発。これにより、有効画素数と同じ146万個のADC、およびデジタルメモリの搭載スペースを確保することに成功したとする。

さらに、146万個のADCの動作に伴って生じる大量のデジタル信号の転送を可能とするリピータ回路も新たに開発。これにより、全画素のデジタル信号を高速に読み書きすることが可能となったという。

これらの技術を組み合わせた結果、ADCをすべての画素の下に配置し、全画素同時に露光したアナログ信号を各々即座にデジタル変換(画素並列A/D変換)した後、デジタルメモリで信号を一時保持することが可能となり、行ごとの読み出し時間のずれによるフォーカルプレーン歪みが解消され、100万画素以上の高感度な裏面照射型CMOSイメージセンサであっても、画素並列ADCによるグローバルシャッター機能を実現することが可能になったと同社では説明している。

なお同成果の詳細は、2018年2月11日から米国サンフランシスコで開催されている最先端半導体チップの研究開発成果に関する国際会議「2018 IEEE international Solid-State Circuits Conference(ISSCC 2018)」にて発表された。