東京工業大学(東工大)は2月12日、富士通研究所と共同で、70GHz~105GHzの周波数範囲(帯域幅35GHz)を用いることで、120Gbps(毎秒120Gbit)の無線伝送を実現したと発表した。

同成果は、同大 工学院電気電子系の岡田健一 准教授らによるもの。詳細は、米国にて2月11日より開催されている最先端半導体チップの研究開発成果に関する国際会議「2018 IEEE international Solid-State Circuits Conference(ISSCC 2018)」にて発表される。

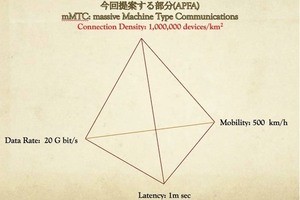

5Gに代表されるように、無線通信技術の高速伝送は着実に進歩してきたが、光ファイバ代替や大規模イベントにおける臨時基地局などでの無線ネットワーク活用に向け、さらなる高速化が求められている。

大容量のデータを無線で伝送するためには、帯域幅を広くとることが重要だが、これまでの3Gや4Gが活用してきた周波数帯域では、さまざまな無線アプリケーションが入り混じり、一度に使える帯域幅に限界があった。そのため、30GHz~300GHzのミリ波帯の活用に期待が集まっているが、CMOSプロセスを用いた集積回路の動作限界に近いところで設計する必要があるため、設計難易度が高く、回路の品質を高めることが難しいという課題があった。実際に研究グループも、2016年に56Gbpsの無線伝送を72~100GHzの周波数範囲で実現していたが、搬送波に含まれる高調波信号により、それ以上、帯域を広げることができないという課題を抱えていたという。

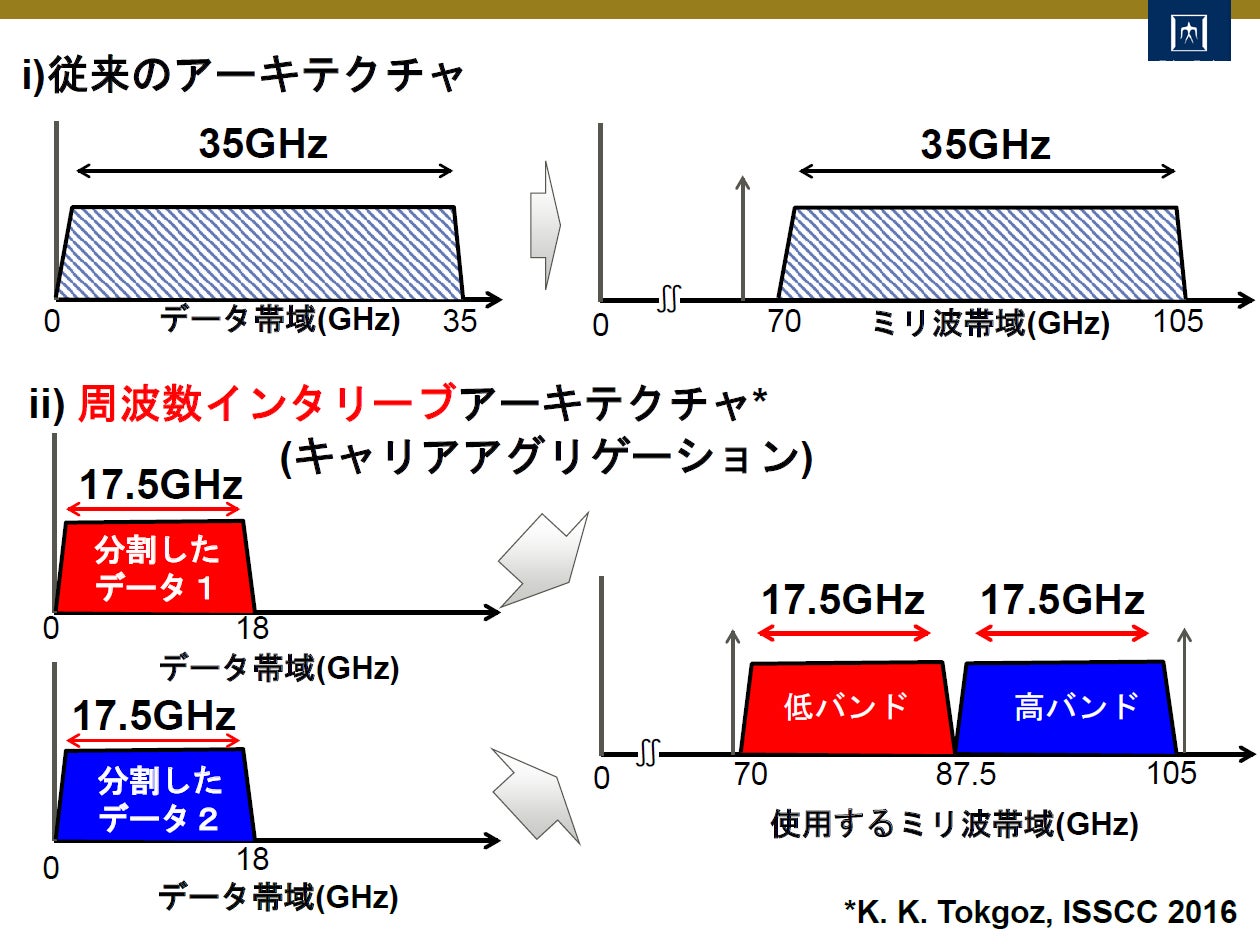

そこで今回、研究グループは70GHz~105GHzの周波数帯域を活用しつつ(35GHzの帯域幅)、一度に35GHzの帯域を扱うのではなく、低帯域信号(70-87.5GHz)と(87.5-105GHz)の2つにデータ信号を分け、それぞれを17.5GHz幅ごろに変復調を行う独自の手法「周波数インタリーブアーキテクチャ」を考案。これにより、高調波信号の低減を実現。35GHz帯域幅で120Gbpsの伝送を可能にしたという。

-

-

-

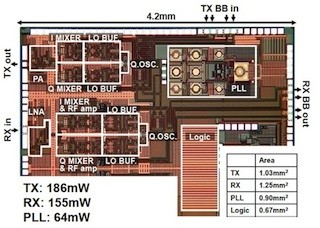

従来は35GHzの帯域幅を一度に処理していたが、今回の研究では、それを2つに分割することで、高速伝送を実現した。また、65nmプロセスを採用したことについて、岡田准教授は、無線機としては最大動作周波数(Fmax)が向上しないといけないが、プロセスを微細化すると必ずしも、Fmaxがあがるかというとそうではなく、むしろ65nmの方が適切な性能を得られるため、と説明している (資料提供:東京工業大学)

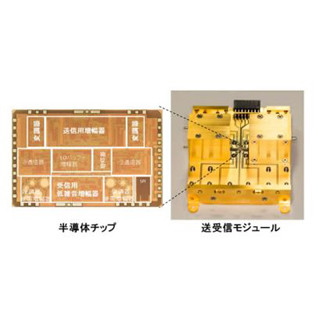

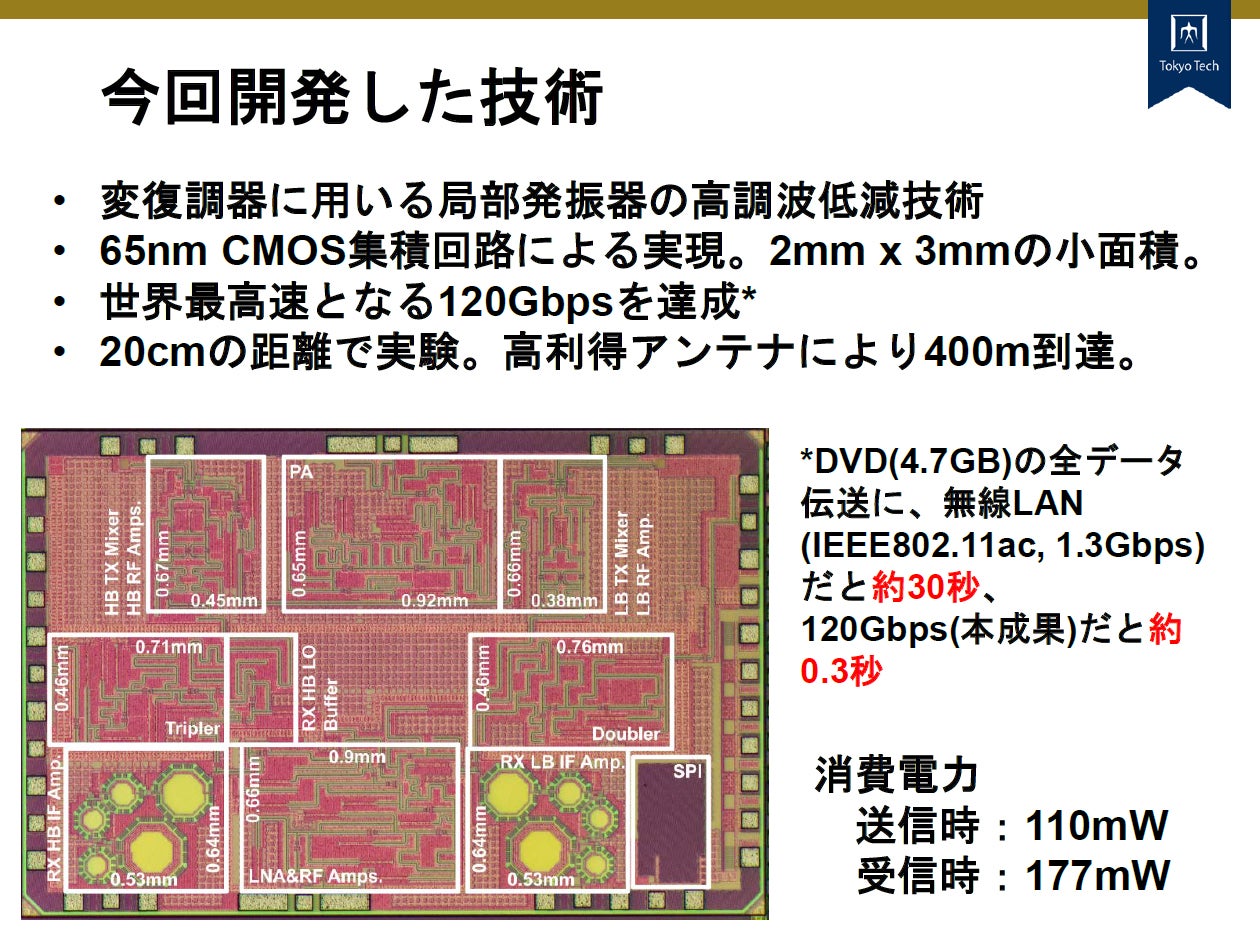

実験のために開発されたチップは、チップサイズ2mm×3mmで65nm CMOSプロセスを採用。室内で20cmの距離を隔てて、2台のモジュールを対向させた実験にて、120Gbpsのデータ転送を、16QAMの多値変調に必要な信号品質を達成しつつ実現したという。この際の消費電力は送信時120mW、受信時160mWで、従来比で約半分に低減できたとする。また、利得の高いアンテナを活用すれば400-600m程度の無線通信が可能になるとのことで(56dBiのアンテナを用いた場合、120Gbpsで400m、100Gbpsで600m)、スマートフォンに搭載して、スモールセルの基地局と通信するといったことも期待できるようになるとする。

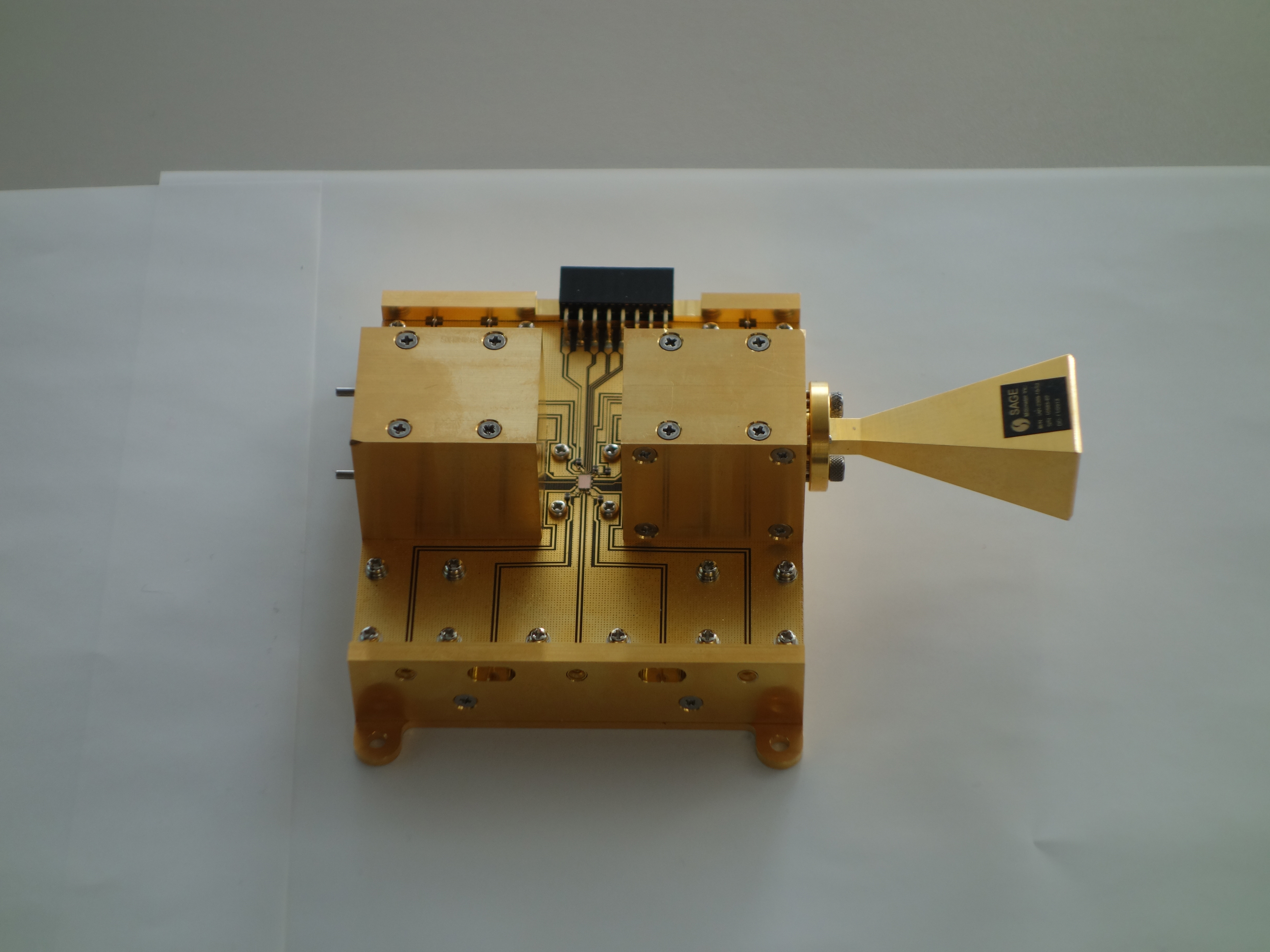

今回の共同研究では、チップ開発を東工大が、送受信モジュールを東工大と富士通研究所が共同で開発しており、基地局間の通信などの回線を手始めにターゲットとし、富士通が2020年ころのビジネス化を目指していく予定だという。