Cadence Design SystemsとArmは10月24日(米国時間)、Armサーバ上でCadenceのSoC@検証ソリューション「Xcelium Parallel Logic Simulation」の先行使用が可能になったことを発表した。

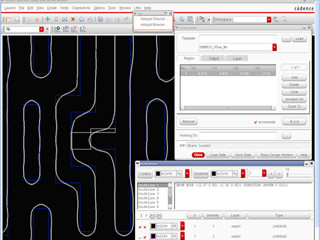

同シミュレーションは、Armサーバ上でネイティブに動作し、EDA処理時間の70%を占めるとも言われるSoC設計の動作検証を実行することが可能。従来のシミュレータと比較して、シングルコアシミュレーションでは最大2倍の高速化、マルチコアシミュレーションでは3倍から10倍の高速化を実現することによりSoC検証時間を短縮し、市場投入期間を全体的に短縮することを可能とするもので、Armサーバ上で実行することで、システム企業および半導体企業はサーバ上のCPUコアを最大限に活用することが可能となり、先端ノード設計に向けて検証の高速化を実現できるようになるという。

具体的には、マルチコアサーバ上での実行に向けて、設計および検証テストベンチの自動パーティショニング機能も提供されるとするほか、シングルコアのジョブを実行する場合、サーバ設置面積単位で見てより多くのXceliumジョブを実行することが可能であったり、長いレイテンシのジョブを実行する場合、より多くのCPUコアを割り当てることで、並列シミュレーション技術を活用したりすることができるようになるという。そのため、両社はArmサーバ上でXceliumを実行することで、最先端のSoC開発に必要となる検証スループットを確保し、かつデータセンターの総所有コストを削減することが可能になると説明している。

なお、Armサーバプロバイダとして、すでにCaviumが自社のThunderX2プラットフォームを、Qualcomm Datacenter Technologiesが自社のQualcomm Centriq 2400プロセッサを、それぞれ活用できることを明らかにしている。