東京工業大学(東工大)は、有限要素法(FEM)と熱回路網の計算手法を用いることで、バンプレスTSV配線では、従来のバンプとTSVを組み合わせた垂直配線方式の3次元積層デバイスに比べて、熱抵抗を30数%(約1/3)まで低減できることが分かったと発表した。

同成果は、同大 科学技術創成研究院 未来産業技術研究所の大場隆之 教授らの研究グループならびにウェハを積層させることで、3次元集積回路を形成するWafer-on-Wafer(WOW)の研究開発を進めている「WOWアライアンス」によるもの。詳細は、4月19日~21日の期間、山形県天童市にて開催された「エレクトロニクス実装国際会議(ICEP2017)」にて21日に発表された。

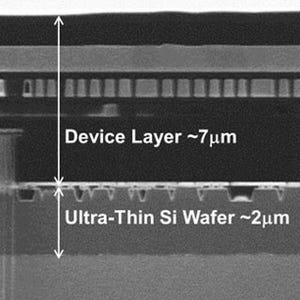

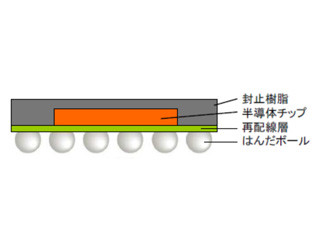

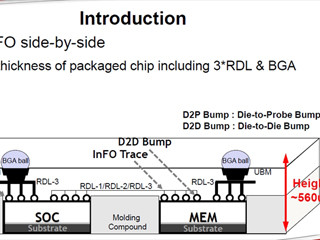

従来のTSVプロセスでは、上下の接続層において、アンダーフィル材料のような絶縁膜、有機膜を使用する必要があり、結果として熱抵抗が大きくなってしまう、という課題があった。今回、研究グループは、3次元積層デバイスの構造を解析することで、BEOL(配線工程:Back End of Line)と垂直方向の接合構造の熱抵抗をFEMにて熱伝導率を推定したほか、全体の熱抵抗についても、熱回路網を用いて推定。この結果、熱抵抗が高い要因の多くがBEOLと垂直配線の接続構造にあることを突き止めたという。

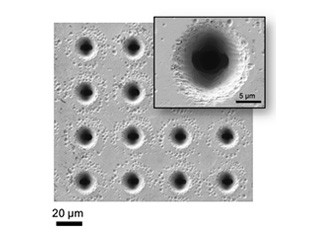

また、バンプレスタイプの熱抵抗の推定も実施。同じバンプレスタイプの垂直方向の接合の熱抵抗は、マイクロバンプタイプと比較して、同じ占有率を想定した場合、150倍小さくなることを推定。この結果、バンプレスTSVの密度を全体の1%程度にまで減らしたとしても、熱抵抗が改善できることが分かり、TSVの本数は信号線として用いられる本数で、放熱性は十分であることが示されたとする。

さらに、これらの結果から、全体の熱抵抗を計算したところ、従来のマイクロバンプ方式では1.54Kcm2/Wであったものを、0.46Kcm2/Wにまで低減できること、ならびに各層の発熱量も踏まえた温度上昇を検討したところ、マイクロバンプタイプでは約20℃の上昇となるが、バンプレスタイプでは約4℃の上昇で済むという推定結果を得たとのことで、これを現行の温度上昇を許容すると仮定した場合、DRAMの積層数は3~4倍に増やすことも可能になると研究グループでは説明している。

なお、研究グループでは今後、薄化ウェハの積層と高密度TSV配線を用いた実証実験を行い、大容量メモリ技術としての実用化を目指すとしている。