|

|

SC16でPost-Kについて発表する富士通の清水氏 |

SC16において、富士通の次世代テクニカルコンピューティング開発本部第一システム統括部長の清水俊幸氏が「ポスト京」スーパーコンピュータ(スパコン)について発表を行った。清水氏は同スパコンのハードウェアの開発責任者である。

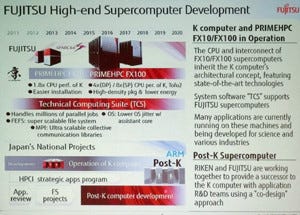

富士通は1970年代からスパコンを作っており、約40年の歴史がある。最近も京コンピュータから、FX10/FX100という後継機を作り、ハードに加えてTCS(Technical Computing Suite)というOS、コンパイラ、ライブラリなどのソフトウェアも開発してきている。

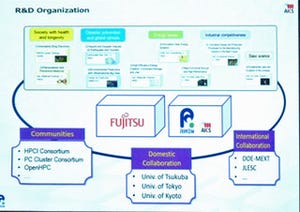

そして、これらの経験をベースに「Post-K(仮称)」の開発に取り組んでいるという。なお、Post-Kは理研との共同開発であり、アプリ開発とのコデザインを行っているとのことである。

|

|

富士通のハイエンドスパコン開発。京コンピュータ、FX10/FX100の経験を基に、理研との共同開発でPost-Kの開発に取り組んでいる (このレポートのすべての図は、SC16での清水氏の発表スライドを撮影したものである) |

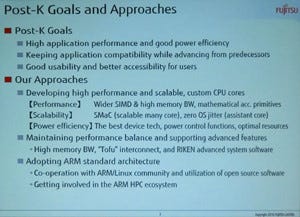

Post-Kの開発目標は、高いアプリケーション性能と良好な電力効率の実現が第一である。そして、京コンピュータとのアプリケーション互換性を維持し、ユーザの使い勝手を改善することも目標に含まれているという。

これらの目標を達成するため、富士通は、独自のカスタムCPUを開発する。Post-KのCPUはARMアーキテクチャであるが、ARMアーキテクチャになるのは主に命令デコードの部分で、基本的なデータ処理を行う部分のマイクロアーキテクチャは、京コンピュータから受け継がれている富士通独自のものであるという。

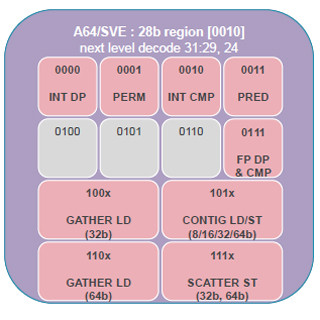

性能的には、SIMD演算幅を512bitに拡張し、この部分ではARMのSVE(Scalable Vector Extension)に準拠している。比較的軽量のOut-of-Orderコアを多数集積し、OSジッタを抑えるためにアシスタントコアを搭載するSMaC(Scalable Many Core)アーキテクチャは、FX100から受け継がれている。

SPARCはオープンアーキテクチャであるがサポータが少なく、SPARC Linuxは富士通が開発せざるを得ない状況に成っている。これをARMアーキテクチャに変えることにより、Linuxはコミュニティのものが利用でき、将来的にはスパコン向けのSVEのサポートもコミュニティで行ってくれる可能性もあるというのが富士通の期待である。

そして、インタコネクトは、京コンピュータで開発したTofuインタコネクトの改良版を使用し、高いメモリバンド幅と理研のシステムソフトウェアと組み合わせて、バランスのとれたシステムを実現する。

なお、ハイエンドスパコンのCPUはARMアーキテクチャに切り替えることにしたが、SPARCアーキテクチャのCPUの開発とビジネス用サーバへの使用は継続するとのことである。

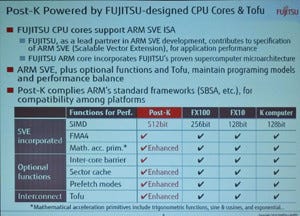

Post-KのCPUは、ARMのSVEをサポートし、倍精度のFMAを8演算並列に実行できる。そして、三角関数などの計算アクセラレータも装備する。さらに、富士通スパコンでサポートされてきたコア間のスレッド実行を同期するバリア機能やセクタキャッシュ、プリフェッチモードなどもFX100より強化されたものを装備する。

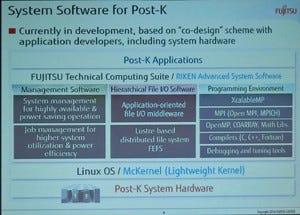

システムソフトウェアは、富士通と理研の共同開発で、McKernelと呼ぶ計算ノード用の軽量カーネルは理研が開発する。

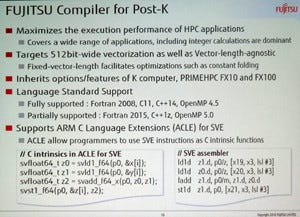

512bit長のSIMD演算器を使うコンパイラは、富士通が開発する。このコンパイラは、ARM C Language Extensions(ACLE)をサポートしており、SVE命令をC言語から使用することが可能になっている。

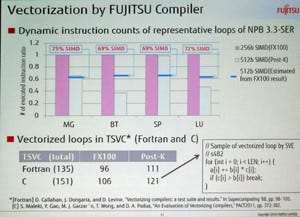

次の図は、NPBベンチマークの4つのプログラムをコンパイルした結果のループ1回あたりの実行命令数を比較したものである。ピンクの棒グラフはFX100の256bit SIMDでコンパイルした場合の命令数で、これを1.0にしている。青線は、FX100の結果からSIMD 512bit化の効果を推定した値を示している。この値は、おおよそ0.6程度になっている。

もう1つの棒グラフは、Post-Kで512bit SIMDでコンパイルした場合の実行命令数である。MGプログラムの場合はほぼ青線と同じであるが、BTとLUでは、青線を下回っている。これはARM SVE命令の効果と考えられる。一方、SPでは青線を上回っているが、これは、まだ、コンパイラにまずいところがあるためであるという。

下の表は、TSVCというプログラムのループの数で、FORTRAN版ソースでは135個のループがあり、FX100のコンパイラの場合は、その内の96ループがベクトル化できた。これに対してPost-Kでは111ループのベクトル化が出来ている。右のようなソースの場合、終了条件がデータ依存でループ回数が分からないので、FX100のコンパイラではベクトル化できない。これに対して、ベクトル長依存性がないSVEでは、ベクトル化できる。このため、15個のループが新たにベクトル化できるようになっている。C言語ソースの場合は、全体が151ループで、FX100では106ループのベクトル化であったものが、Post-Kでは121ループがベクトル化できている。

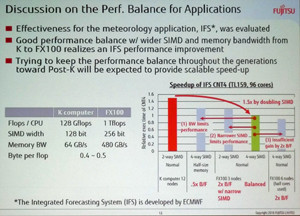

次の棒グラフは性能バランスを示すもので、左端の赤い棒は2Way SIMDのFX100実行時間で、左から3本目の薄い赤のグラフがPost-Kに相当する4Way SIMDの演算器を搭載し、メモリバンド幅を倍増したマシンの実行時間である。この2つのグラフを比較すると、Post-K相当はFX100の約1.5倍の性能である。

左から2本目の棒グラフはPost-Kの構成のメモリバンド幅を半減したもの、その右はメモリバンド幅はそのままで、2Way SIMDと演算能力を半減したもので、Post-K相当の構成より20%程度性能が下がっている。

右端の棒グラフは、Post-K相当からさらにメモリバンド幅を倍増したケースであるが、10%程度の性能向上に留まっている。

ということで、Post-Kの演算性能とメモリバンド幅はバランスが取れていると結論付けている。ただし、これはIFSという気象系のアプリケーションを実行した場合で、すべての計算にこれが当てはまるとは限らないと考えられる。

|

|

IFSという気象アプリを実行するケースで、Post-K相当の構成から、演算性能、あるいはメモリバンド幅のどちらか一方を半減すると、性能は20%低下。しかし、メモリバンド幅を倍増しても10%程度の性能向上であり、バランスが取れているという |

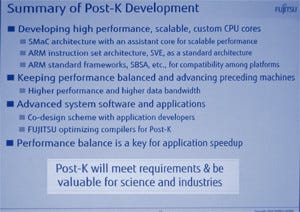

Post-Kの開発のまとめであるが、スケーラブルメニーコア(SMaC)アーキテクチャのカスタムコアプロセサを開発する。これまでのSPARCアーキテクチャに変えてARM v8のSVE拡張命令セットをサポートし、ARMの標準フレームワークであるSBSAもサポートし、ARMサーバとの互換性を持たせる。

マイクロアーキテクチャは、京コンピュータからの資産を受け継ぎ、バランスのとれたマシンを目指す。

コデザインで実アプリケーションの開発者が使い易く、実アプリケーションで実行性能が出せるマシンを目指す。そして、そのためには、バランスのとれた設計とすることが重要であるという。

そして、Post-Kは、設計目標を満たし、科学界にも産業界にも役に立つマシンになる、と述べて発表を締めくくった。

会場から、完成時期の質問が出たが、2020年というオリジナルの目標に対して、1~2年遅れるというのが、現在の公式見解と答えていた。