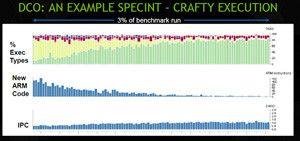

次の図は、実行開始の3%の期間の拡大図で、当初は大部分がARMコードの実行であるが、変換が進むにつれて、徐々にマイクロコードの実行が増えている。また、それに伴ってIPCも改善してきている。

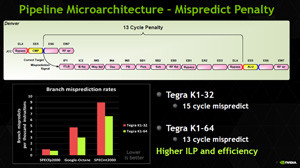

分岐予測に関しては、Cortex A15は分岐予測が間違った場合の訂正には15サイクルを必要とするが、Denverは13サイクルである。また、左下のグラフは1000命令あたりの分岐予測ミスの回数を比べたもので、Denverコアの方が予測ミスが少ない。この2つの違いだけで性能に大きな差が付くとは考えられないが、Denverの方が良いことは確かである。

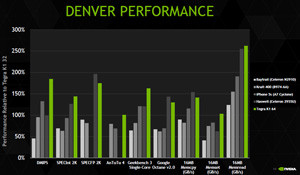

これらの動的最適化などによる性能改善効果であるが、Denverの性能として次の図が示された。Tegra K1-32を100%とした相対比較であり、棒グラフは左から順にIntelのCeleron N2910、QualcommのKrait-400、AppleのA7、IntelのCeleron 2955U、そして、右端がTegra K1-64である。比較に使用したプログラムとしてはDhrystone(DMIPS)、SPECint、SPECfpなどである。

Denverは、SPECintベンチマークではTegra K1-32の140%強の性能で、HaswellベースのCeleron 2955Uを若干上回る性能である。一方、SPECfpではTegra K1-32の1.75倍であるが、Celeron 2955Uには若干劣る結果で、まあ、Celeron 2955U(1.4GHz、2MBキャッシュ)と同程度の性能と言える。一方、Atom系のCeleron N2910やKrait-400、A7などスマホ用のプロセサよりも性能が高い。

Celeron 2955Uと同程度の性能で、デスクトップ並の性能は多少言い過ぎの感もあるが、他社のモバイルプロセサと比べて負けない性能である。

性能と並んで重要なのが消費電力である。Tegra K1-32ではCortex A15コアをもう1個追加し、そのコアは低リーク電流トランジスタを使って作るということを行っている。仕事が少ない状態では通常のA15コアはパワーゲートで電源を切り、低リークの5番目のコアを使えば、リーク電流が少なく低電力が実現できる。

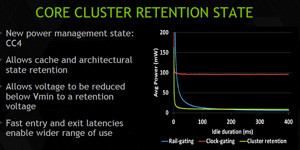

これに対して、Tegra K1-64では、レジスタやキャッシュの状態を維持できる限界まで電源電圧を下げるという方法でアイドル時の電力を削減している。

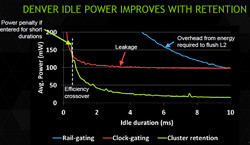

次の図のグラフの緑の線はクロックゲートで動作を止めた場合の消費電力を示しており、リーク電流が流れるので、100mW程度の電力を消費し続けている。青線はパワーゲートを行った場合で、アイドル期間が200msより長い場合は10mW以下の消費電力となっている。

これに対してレジスタやキャッシュのデータ保持限界まで電源電圧を下げるという方法は、パワーゲートとはほぼ同等レベルに消費電力を減らすことできている。

パワーゲートはリーク電流は小さいが、電源を切るとキャッシュの内容が消えてしまうので、電源をオフにする前に、2次キャッシュに残っている情報をメインメモリに書き出しておく必要があり、このために電力を必要とする。この消費電力を含めたのが次の図で、パワーゲートがクロックゲートの消費電力を下回るには10ms以上のアイドル時間が必要である。これに対してDenverの方法では、アイドル時間が0.5msより長ければクロックゲートよりも消費エネルギーが小さい。

アイドル状態では、レジスタとキャッシュの情報を保持できる限界まで電源電圧を下げるというDenverの方法は、比較的短いアイドル時間でもエネルギー消費が小さく、長いアイドル時間でもパワーゲートに近い消費エネルギーに抑えられるということで、明確には述べられなかったが、Tegra K1-64チップには、低リークコアのような特別なコアを搭載していないと思われる。