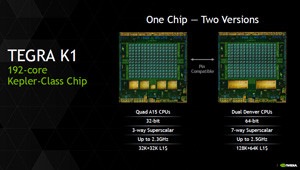

Hot Chips 26においてNVIDIAは、自社開発の高性能64bit ARMコアである「Denver」を発表した。2014年の1月にNVIDIAは、ARMコアと192CUDAコアのKepler GPUを集積するモバイル用SoCであるTegra K1チップを発表した。最初の製品は、ARMコアとしては32bitアーキテクチャのCortex A15コアを4コア搭載するものであるが、自社開発のDenverという64bitアーキテクチャのコアを2コア搭載するものも、2014年の後半には登場すると発表されていた。

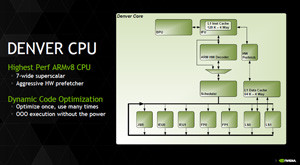

Denverであるが、64bit ARMv8命令をサポートする7wayのスーパスカラプロセサで、128KBの1次命令キャッシュと64KBの1次データキャッシュを持ち、クロックは最大2.5GHzと発表されている。

なお、次の図のチップ写真のように見えるものは、ブロックダイヤに基づいてそれらしく描いた絵で、偽物である。NVIDIAが自社のマーケティングに使うのは勝手であるが、本物のチップ写真を載せることになっている学会発表資料にこの絵を使うのはルール違反であろう。

|

|

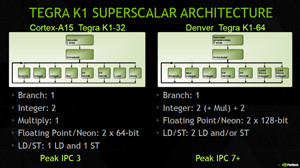

A15コアを使うTegra K1-32とDenverコアを使うTegra K1-64チップのプロセサコアの比較。チップ写真は偽物で、意味がない。(出典:この記事のすべての図は、Hot Chips 26におけるNVIDIAのBoggs氏の発表スライドの抜粋である) |

次の図はDenverプロセサのブロックダイヤであるが、7つの実行パイプラインを持つ変哲もないプロセサという感じである。しかし、ARM HW Decoderというブロックをバイパスするパスが設けられている点がミソで、これが高い性能を引き出す仕掛けになっている。

32bitのCortex A15コアと比較すると、実行ユニットの構成はあまり差はないのであるが、A15はピークで3命令であるが、Denverではピークでは7命令以上実行できると書かれている。ただし、これはピークの話で、後に出てくる性能比較では、これほど大きな性能の違いはない。

命令発行数の違いは、Denverが動的にコードを最適化し、最適化コードを実行する場合は、ARM HW Decoderをバイパスして、Denverのネーティブのマイクロコード命令を最大8命令並列にスケジューラに発行する機能を持っているからである。

Denverはメインメモリに最大128MBの「Optimization Cache」と呼ぶ領域を確保し、ARM命令を実行中にプロファイルデータを取得して、ループのアンロールや無駄な命令を削除などのコンパイラが行う一般的な最適化に加えて、レジスタのリネーム、ロードストア命令の順序の入れ替えなど実行しやすいように最適化したマイクロコードに変換してOptimization Cacheに格納する。これを「Dynamic Code Optimization」と呼んでいる。

このネーティブコードへの変換をキャッシュするやり方は、かつてのTransmetaのCrusoeと同じであるが、Crusoeはx86命令をエミュレーションしていたのに対して、Denverでは、毎サイクル2命令であるが、ハードウェアでARM命令を直接実行できるので、変換オーバヘッドが小さいという点が異なる。

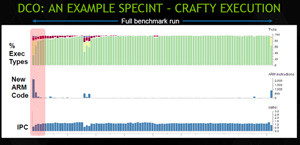

次の図はSPECintベンチマークの中のCraftyというプログラムの実行状況を示すもので、一番上の図で、上辺にある濃い部分がオプチマイザが走っている部分、下辺から上に伸びている棒グラフがOptimization Cacheのマイクロコードを実行している部分、そして、地のように見える黄色い部分がARMコードを実行している部分である。最初はARMコードの実行が多く、ある程度オプチマイザも走っている。しかし、全体的に見ると、ネーティブのマイクロコードを実行している時間が大部分となっている。

中間の棒グラフは新しいARMコードの実行比率で、下の棒グラフはIPC(相対値)である。