筑波大学計算科学研究センターの「HA-PACS/TCA」は、2013年11月のGreen500で3位となったスパコンシステムである。10コアの「Xeon E5-2680v2」2ソケットに4基の「NVIDIA K20x」GPUを接続した計算ノードを使っているが、16ノードを独自開発の「PEACH2」というデバイスを使って密結合したアクセラレータ(Tightly Coupled Accelerators)となっていることが特徴である。

|

|

HA-PACS/TCAを発表する東大の塙特任准教授 |

このTCAについて、東京大学(東大)の塙敏博 特任准教授がGTC 2014で発表を行った。塙先生は筑波大でTCAを開発しておられたのであるが、2013年12月に、東大情報基盤センターに移られたとのことである。

HA-PACS(Highly Accelerated Parallel Advanced system for Computational Sciences)は、エクサフロップスの実現に向けて筑波大が行っている、演算加速装置を中心とする超並列計算機におけるアプリケーションおよび多数の演算加速装置を効率的に結合する並列システムの研究開発プロジェクトの実証システムである。また、TCA機構の通信システム・ソフトウェアについてはJST-CREST「ポストペタスケール時代に向けた演算加速機構・通信機構統合環境の研究開発」研究(課題代表:筑波大学・朴泰祐教授)において開発が進められている。

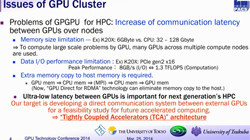

GPUはGreen500の1位から10位を独占するほど多くのグリーンスパコンに使われているが、GPUのメモリサイズが限られる、データIOのバンド幅が限られる、CPUメモリとのデータのコピーが必要などの問題がある。

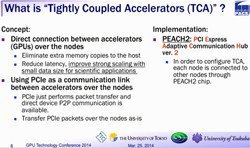

これらの問題を解決するため、筑波大が開発したのが、PCI Expressをデータリンクとして使って計算ノード間を密結合するTightly Coupled Acceleratorsという構造である。このため、筑波大は、ノード間の通信ハブとなるPEACH2というチップを開発している。なお、初代のPEACHはASICであったが、PEACH2はAlteraのFPGAで実現されている。

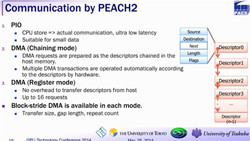

図3はPEACH2チップのブロックダイヤグラムで、東西南北の4ポートとそれらの間を接続するルーティング機能とDMAエンジンを内蔵する。

NポートはPCIeボードのコネクタで、計算ノードに接続される。その他のポートは他のPEACH2ボードのEWSポートに接続されるが、EWポートはリングを構成するように接続され、Sポートは他のリングとの接続に使われる。

TCAでは8計算ノードの2つのリングをSポートで接続し、16計算ノードを1つのTCAサブクラスタとしている。

PEACH2を使った通信は、CPUから他のノードメモリへのPIOとメモリ間のDMAが可能であり、DMAはメモリ上にDMAディスクリプタのリンクチェインを作る方法と、PEACH2チップ内のレジスタで最大16個のディスクリプタを格納する方法がある。後者はディスクリプタの個数が制限されるが、メモリからディスクリプタを読む必要がない分、オーバヘッドが小さい。そして、それぞれのディスクリプタでは転送のブロックサイズ、ギャップ長、繰り返し回数を指定でき、3次元配列を部分的にコピーするのに適した構造となっている。