ベルギーIMECとルネサス エレクトロニクスは、次世代広帯域無線規格であるLTE-Advancedや次世代Wi-Fi(IEEE802.11ac)の受信用途に向けて、電力効率と変換速度を改善した逐次比較型(SAR)アナログ/デジタル変換器(SAR-ADC)を共同で開発したことを発表した。同成果の詳細は、2012年2月19日から米国サンフランシスコで開催されている「国際固体素子回路会議(ISSCC:International Solid-State Circuits Conference)」にて、2月22日(現地時間)に発表された。

SAR-ADCは、高電力効率で省面積という特徴から無線用途の幅広い応用分野で魅力的なデバイスとなっており、特に、中速・中精度の応用に適した方式とされている。しかし、次世代広帯域無線規格であるLTE-advancedや次世代Wi-Fi向け受信機には、より高速なADCが必要とされており、性能の向上が求められていた。

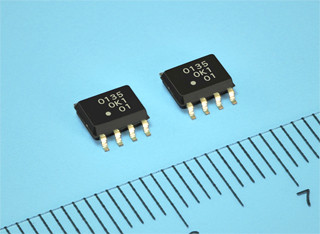

今回両社が開発した新しいSAR-ADCの方式は、より高速かつ低消費電力のADCを省面積で実現したいという要求に対応したもので、同クラス(変換速度250MSps、有効ビット(ENOB)9.5ビット)では世界最小級となる消費電力1.7mWを実現しているほか、11ビットの精度、フルダイナミック、2チャネル・インターリーブ&2ステージ・パイプラインSARにより、250MSpsの変換速度時で10fJ/conversion-stepの電力効率を実現している。

この効率は、IMECが以前開発していた草分け的なAD変換方式をベースとした設計と、先端CMOSテクノロジを用いた試作により得られたもので、設計では、完全にダイナミックな回路構成とすることで消費電力がサンプリング周波数に比例し無駄がないこと、最大限にデジタル化することで比較器だけを唯一のアナログ回路ブロックとしたこと、が特徴だという。

一方、プロセスには40nm CMOSプロセスを採用。試作したADCのチップサイズは、0.066mm2で、測定結果は、微分直線性誤差(DNL)が0.8/-0.5LSB、 積分直線性誤差(INL)が1.1/-1.5LSBであった。また、動特性としては、10MSps時のSNDRが62dBで、有効ビット(ENOB)に直すと10.0ビットとなる。変換速度を上げても、有効ビットは250MSpsまで9.5ビット以上を維持したという。さらに、消費電力は、1変換あたり6.9pJoule(10MSps時70μW、250MSps時1.7mW)を実現、結果、7~10fJ/conversion-stepの電力効率を達成している。

このほか両社は、RF部全体とADCを接続するための新しい手法も開発。同手法は、電圧ドメインのADCシステムにおける大きな入力容量の充放電による消費電力増大を避けて受信システム全体の電力効率を改善するために、3.2-51.2mSiemensの範囲で可変可能な電流ドメインの可変ゲイントランスコンダクタ(VGA)が電荷ドメインのSAR-ADCを駆動するように使われているとのことで、それにより、無駄な電力消費をなくすことが可能となり、システム全体の消費電力の低減が可能になったという。40nmCMOSで試作した10ビット80MSpsのVGA+ADCでは、70dBのダイナミックレンジを有しつつも、電源電圧1.1Vで5.45mA以下の電力性を達成している。