大手FPGAベンダである米Altera社は1月24日(米国時間)、28nmプロセスを採用したFPGA製品ファミリの全体像を発表した。これに先立つ1月19日(日本時間)に、日本法人の日本アルテラは東京・新宿のホテルで報道機関向けの先行説明会を開催した。

先行説明会では、米Alteraのバイス・プレジデントと日本アルテラの代表取締役社長を兼務する日隈寛和氏が、初めに挨拶した。日隈氏は現行製品の最先端世代である40nmプロセス品の出荷を2008年に開始し、現在では65nm/40nm世代の製品がAltera全体の売り上げの40%を超えるようになったと述べていた。また28nmプロセスの製品ファミリは「V(ファイブ)」の名称で統一されており、「勝利(Victory)」の「V」の意味も込められていると語った。

続いて米Alteraのプロダクト・マーケティング担当シニア・ディレクタを務めるDavid Greenfield氏が、製品ファミリの全体像を説明した。

|

|

|

米Alteraのバイス・プレジデントと日本アルテラの代表取締役社長を兼務する日隈寛和氏 |

米Alteraのプロダクト・マーケティング担当シニア・ディレクタを務めるDavid Greenfield氏 |

Greenfield氏は、様々な要素技術の組み合わせによってFPGAに対する要求の多様化に応えていく必要があるとし、Alteraでは「プロセス技術」、「トランシーバ技術」、「製品アーキテクチャ」、「システムIP」の4つの要素技術でユーザーの要望にかなう製品を提供していくと説明した。

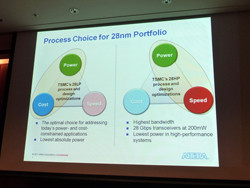

Alteraはシリコン半導体製品の製造工場を持たないファブレス企業であり、大手ファウンドリ企業である台湾TSMCに製造を委託してきた。28nm世代のプロセス技術も、TSMCが開発したプロセスである。プロセス技術については昨年(2010年)12月7日に発表した内容と同様で、TSMCの28nm High Performance(HP)プロセス技術と28nm Low-Power(LP)プロセス技術の両方を採用すると説明していた。

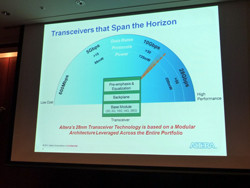

トランシーバ技術では、最大で28Gbpsのデータ転送速度(バンド幅)を備える高速トランシーバ回路技術を28nmプロセス製品で用意する。10Gbpsのトランシーバ回路や5Gbpsのトランシーバ回路なども用意することで、幅広い要求に応える。

製品アーキテクチャでは、3種類の内蔵メモリ・アーキテクチャ、データ転送速度の異なるメモリ・コントローラとI/Oブロックを用意することで、多様な要求に適切に対応する。システムIPでは、重要な応用分野に向けたハードマクロを自社開発していく。特に通信/ネットワーク向けIPの開発では、2010年12月に買収を発表したIPベンダーのAvalon Microelectronicsを活用する。

|

|

|

|

3種類の内蔵メモリ・ブロック。バッファ用のM10K、データ用のM20K、汎用のMLABがある |

低コスト用途向け、ミッドレンジ用途向け、広帯域用途向けのメモリ・コントローラを用意した。代表的な応用事例(暗視ゴーグル、ビデオ・スイッチ、超高速イーサネット・スイッチ)を併記してある |

I/Oブロックも低コスト向け、ミッドレンジ向け、高性能向けを用意した |

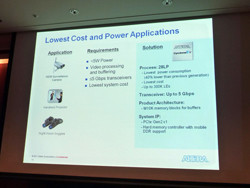

具体的な製品ファミリでは、低コストおよび低消費電力を追求するローエンド向けにFPGA製品ファミリ「Cyclone V」を用意する。プロセス技術は28nm LPプロセス、トランシーバ技術はバンド幅5Gbpsのトランシーバ、内蔵メモリ・ブロックはバッファ用のM10Kである。入出力ではモバイルDDRを含めたメモリ・コントローラやPCI Express Gen2 ×1レーンなどをサポートする。Cyclone Vシリーズの最初の製品は、2012年の第1四半期に出荷を始める予定となっている。

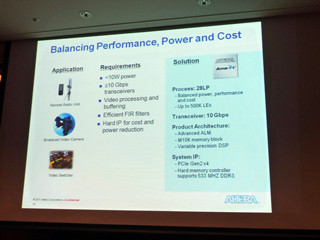

性能と消費電力、コストのバランスを重視するミッドレンジ向けには「Arria V」を用意する。プロセス技術は28nm LPプロセス、トランシーバ技術はバンド幅10Gbpsのトランシーバ、内蔵メモリ・ブロックはバッファ用のM10Kである。またDSPのハードマクロを内蔵する。入出力では533MHzのDDR3メモリ・コントローラやPCI Express Gen2 ×4レーンなどをサポートする。Arria Vシリーズの最初の製品は、2011年の後半に出荷を始める予定となっている。

|

|

28nm世代のミッドレンジFPGA「Arria V」の用途と要求仕様、製品概要。現行世代品は40nmプロセスの「Arria II」である。製品シリーズ名の数字を「V」に統一するため、「III」と「IV」は欠番となった |

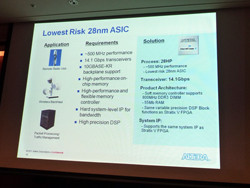

高性能を追求するハイエンド向けFPGAの「Stratix V」は、28nm世代の最初の製品シリーズとして2010年4月20日に発表済みである。プロセス技術は28nm HPプロセス、トランシーバ技術はバンド幅28Gbpsのトランシーバ、内蔵メモリ・ブロックはデータ用のM20Kである。また54×54bitの可変精度DSPブロックをハードマクロとして内蔵している。入出力ではPCI Express Gen3 ×8レーンや100Gイーサネット、Interrlakenなどをサポートする。Stratix Vシリーズの最初の製品は、2011年第1四半期にエンジニアリング・サンプルが出荷される予定である。現在のところ、開発は順調に進んでいるとGreenfield氏は説明していた。

このほか、「Stratix V」をASIC化した「HardCopy V」を用意することを明らかにした。HardCopy Vシリーズは、Stratix Vと同様の28nm HPプロセスで製造するほか、Stratix Vと同じ可変精度DSPブロックを搭載する。