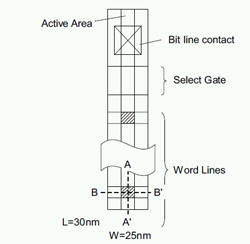

東芝とSanDiskは、30nmと微細なプロセスによるフローティングゲート(FG)型NAND型フラッシュメモリセルを共同で試作し、その評価結果をIEDM 2008で明らかにした(講演番号34.1)。シングルレベルセル(SLC)で32Gビット、マルチレベルセル(MLC)で64Gビット以上の大容量NAND型フラッシュメモリに向けたセル技術とみられる。

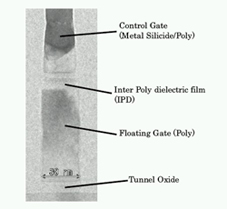

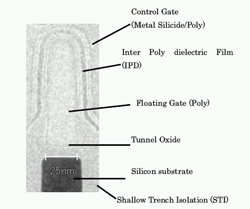

試作したNAND型フラッシュメモリセルはゲート長が30nm、ゲート幅が25nmときわめて微細である。制御ゲートとフローティングゲートの間にある中間絶縁膜の厚みを11nmと薄くすることで制御ゲートとフローティングゲートの間の容量結合を強めた。なお前世代の43nmプロセスにおける中間絶縁膜の厚みは13nmだった。

フローティングゲート型セルの微細化では、隣接セル間の容量結合が問題になる。今回は隣接セル間の絶縁膜材料を酸化膜とし、窒化膜に比べて隣接セル間の容量結合を弱めた。

|

|

|

NAND型フラッシュメモリセルの断面観察写真。レイアウトのA-A'方向で切断した断面である(IEDM 2008の論文集から抜粋) |

NAND型フラッシュメモリセルの断面観察写真。レイアウトのB-B'方向で切断した断面である(IEDM 2008の論文集から抜粋) |

メモリセルの書き込み特性は20V、100μsの書き込みパルスでしきい電圧がプラス5V、消去特性は16V、1msの消去パルスでしきい電圧がマイナス3Vである。書き込み飽和時のしきい電圧はプラス7V、消去飽和時のしきい電圧はマイナス7Vで、最大で14Vと広いウインドウを確保できた。この結果、3ビット/セル以上のスーパーマルチレベルセル(S-MLC)にも対応できるとした。

書き換え寿命特性では、1万回の書き換えを繰り返してもウインドウの変化はほとんどみられなかった(ウインドウの初期値は4V、温度は絶対温度300℃)。データ保持特性では、4値のMLCに対して1000時間を経過してもしきい電圧の変化は0.4V未満にとどまった(温度は85℃)。

また論文集には掲載されていないものの、講演ではしきい電圧を7通りに書き込んだセルのバラつき特性を示すグラフが示された。グラフを見る限りはきれいに書き込まれており、3ビット/セルのS-MLCに適用できる可能性が少なくないことが理解できた。