RTLでの消費電力低減

RTLは具体的な半導体製造条件に依存しない設計レベルで、信号、クロック、データ、メモリ、演算などの要素を設計言語(Verilog HDLやVHDLなど)で記述したものである。

このレベルでは電源そのものの制御はできないが、回路ブロックごとに動作させるか否かを指定できるようにし、その組み合わせをモードで分けて動作を制御する。

例えば、次の表1のように分けて考える。

表1 RTLで回路ブロックごとに動作のON/OFFを考慮して制御する例

| モード | プロセッサ | レジスタバンク | 状況 |

|---|---|---|---|

| 1:フル動作 | ON | ON | 完全動作 |

| 2:スタンバイ | ON | OFF | 高速復帰可能 |

| 3:シャットダウン | OFF | OFF | スリープ状態 |

低消費電力化の考え方の基本は、ある状況において必要な回路ブロックを動作させ、不必要なブロックは停止させるというものである。

表1の例では、『モード1』はフルに動作している状態で、すべての動作に対応している。「モード2』は動作は休みになっているが即復帰が可能という状態で、『モード3』はしばらく動作する必要がない状態である。当然ながら、モード3が最も消費電力が低い状態だが、動作が必要になった場合には復帰までに時間がかかる。

一般にRTLはクロックによって制御されている。つまりクロックが動作している部分は回路自体も動作し、クロックを止めた部分は回路自体も停止している。動作している部分は当然ながら電力を消費する。したがって、表1の例では、3つのモードについてクロックを動作させるかどうかで制御する。

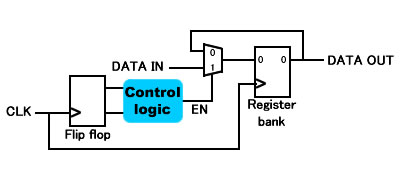

クロック動作の制御には、図6ようなクロックゲーティングをRTLに記述しておくか、または市販の設計自動化ツールを使い、後の論理合成時にクロックゲーティングを挿入する方法がある。なお、論理合成とは具体的な製造条件を入れたセルライブラリへのマッピングと最適化を行うことである

|

図6 クロックゲーティングの例 |

低消費電力対応の少し進んだ考え方として、回路ブロックごとに異なる電源電圧系統にし、個別の電源設定を可能にするという方法がある。電源付加の方法は、単純には電源を入れるか入れないか(ON/OFF)というものと、さらに進んで電源電圧の値を変えるものとがある。

RTLには電源とアースのラインがないので、電源電圧の変更をRTLのみで実施することができない。そこで、RTLからの論理合成の際に電源とアースのラインを複数組設けるなどの方法で、回路によって異なる電圧を与えることを可能にする。

また、回路ブロックごとに異なる電源電圧にすると、回路ブロックのポートを接続する際に異なる電圧に対応するためのレベルシフタが必要になる。これは論理合成用のセルライブラリ中のコンポーネントとして用意する。最近の設計自動化(EDA)ツールでは、このレベルシフタを自動的に挿入する機能を備えているものがある。

回路ブロックごとに電源ON/OFFの設定が可能になると、表1を拡張して、動作のOFF状態にクロック停止と電源ON/OFFを組み合わせることができる。これにより、柔軟な消費電力設定が可能になる。ここで留意すべきこととして、クロック停止のみではリーク電流が残っており、最近のLSIではこのリーク電流が割合として大きくなっていることがある。しかし電源OFFが可能になると、消費電力をほぼゼロの状態にできる。ただし、電源OFFからの復帰はクロック停止のみの場合より時間がかかる(場合によってはリセットに近い動作になる)ということに注意が必要である。

ここまで述べたRTLでの消費電力の考慮および設計は、ARMが提供するIPコアにおいて実現されている。