インメモリコンピューティング

インメモリコンピューティング分野からはIBMの論文が注目論文に選ばれた。

線形CCOを用いたAD変換器アレイおよびデジタル処理部を搭載した相変化メモリに基づくインメモリコンピューティングコア(論文番号:JFS2-5)

“HERMES Core - A 14nm CMOS and PCM-based In-Memory Compute Core using an array of 300ps/LSB Linearized CCO-based ADCs and local digital processing,” R. Khaddam-Aljameh, et al., IBM Research Europe & IBM Research, Albany & IBM Systems and Technology & IBM T. J. Watson Research Center

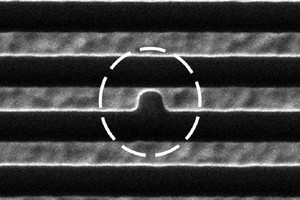

IBMは14nmプロセスによる相変化メモリ(PCM)を利用した256×256アレイ構成を持つインメモリコンピューティングコアについて発表する。

コアユニットには線形電流制御型発振器(Linearized CCO)を用いることで4μm間隔に配置可能な256台のAD変換器および、ディープラーニングに用いられるアフィンスケーリングとReLU演算を実行可能なデジタル処理部を搭載している。新規技術として1GHzまで動作可能な線形周波数変換回路を用いることで、高精度な行列ベクトル乗算を実現している。

2つのコンピューティングコアを結合することで、MNISTおよびCIFAR-10データセットを用いた推論処理を実証し、エネルギー効率として10.5TOPS/W、面積性能として1.59TOPS/mm2を達成している。

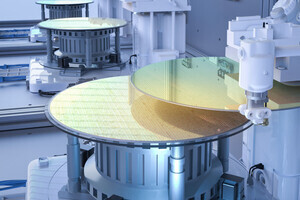

メモリ技術

メモリ技術分野ではTSMCの論文が注目論文に選ばれた。TSMCは、顧客支援のための図抜けたIC設計力を身に着けてきていることがうかがえる。

5nm High-k/メタルゲートFEFET製造プロセスによるアンチヒューズ型16Kbワンタイムメモリ(論文番号: C16-1)

“A 16Kb Antifuse One-Time-Programmable Memory in 5nm High-K Metal-Gate FinFET CMOS Featuring Bootstrap High Voltage Scheme, Read Endpoint Detection and Pseudo-Differential Sensing,” Shaun Chou, et al., TSMC

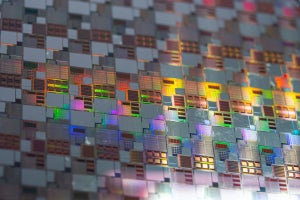

TSMCは世界初の5nm Higk-k/メタルゲートFinFET製造プロセス向けのアンチフューズ型16Kbワンタイムメモリ(OTP)を発表する。

ブートストラップ型の高電圧生成技術(Bootstrap High Voltage Scheme:BHVS)、書き込みエンドポイント検出(ReadEndpoint Detection:REPD)、疑似差動読み出し(Pseudo-Differential Sensing:PDS)を実装することにより、SoCの出荷後プログラミングにおいて1ppb以下のエラーレートおよび、125℃環境下で10年間のデータ保持を実証した。

ヘテロジニアス・3D集積技術分野

ヘテロジニアス・3D集積技術分野では、MediaTekの論文が、注目論文に選ばれた。

異なる種類のチップ集積のための高密度、低電力、7nmCMOS チップ間通信技術(論文番号:JFS-1-3)

“A 7nm 0.46pJ/bit 20Gbps with BER 1E-25 Die-to-Die Link Using Minimum Intrinsic Auto Alignment and Noise-Immunity Encode,” Ying-Yu Hsu, et al., MediaTek

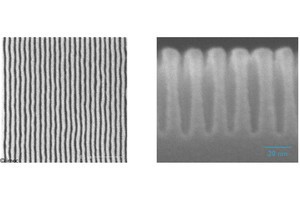

この論文では、高密度、低エラー率、低電力の超短距離(USR:ultra-short-reach)チップ間通信のためのMlink(MediaTekリンク)の物理層を提案している。

提案するMlinkはTSMCの7nm FinFET ポリシリコン1層メタル15層CMOS プロセスで製造されている。チップ間の物理的接続はTSMCのCoWoS(Chip-on-Wafer-on-Substrate)およびInFO(Integrated Fan-Out)パッケージング技術を用いて実現されており、物理層は終端なしシングルエンドの1/4レートストロープとアンバランススキーム採用したトランシーバ、タイミングのずれが本質的に最小となる自動アライメント技術、ノイズ耐性の高いコーディング技術を採用し高エネルギー効率、高性能なシステムを実現している。

1mmの短距離通信時に、信号配線1本あたり20Gb/sで 0.46pJ/bitを達成し、エラーレートは10-25を目指しているほか、信号幅の密度は、単位長さあたりでは5.31Tb/s/mm、単位面積当たりでは2.25Tb/s/mm2となっている。

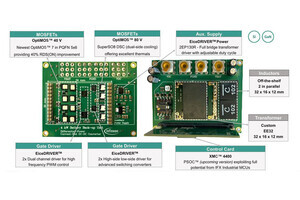

パワーコンバージョン回路

パワーコンバージョン回路分野では、IntelおよびUCLAの2件の論文が注目論文に選ばれた。

サーバ応用向け5V入力1V出力DC-DCコンバータをパッケージ内に集積したGaNパワーモジュール(論文番号:C3-1)

“A 32A 5V-Input, 94.2% Peak Efficiency High-Frequency Power Converter Module Featuring Package-Integrated Low-Voltage GaN NMOS Power Transistors,” Nachiket Desai, et al., Intel

Intelは、シリコントランジスタより5-10倍優れた性能の低電圧GaNパワートランジスタとCMOSドライバICを4mm×4mm のパッケージ内に集積した高周波・高電流密度(9A/mm2)のバックコンバータを提案する。スイッチング周波数3MHz、5V入力1V出力の動作において、コンバータの最大電力変換効率は94.2%を達成した。

20.3fsジッタを実現する19GHz帯PLL(論文番号:C18-1)

“A 19-GHz PLL with 20.3-fs Jitter,” Yu Zhao and Behzad Razavi, UCLA

米国カリフォルニア大学ロサンゼルス校(UCLA)は28nmプロセスで作成した超低ジッタPLLを発表する。

両エッジサンプリング技術とタイミング制御技術を組み合わせることで、20.3fsのジッタ性能を実現している。250MHzの入力基準周波数に対して、12mWの消費電力で19GHzの発振周波数の出力を可能としている。