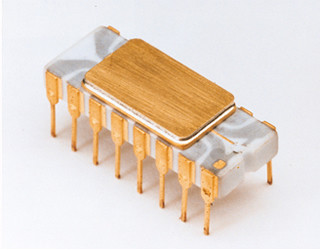

本連載はHisa Ando氏による連載「コンピュータアーキテクチャ」の初掲載(2005年9月20日掲載)から第72回(2007年3月31日掲載)までの原稿を再掲載したものとなります。第73回以降、最新のものにつきましては、コチラにて、ご確認ください。

多少、話は横道にそれるが、状態割り当てについて述べてみたい。4004のタイミング発生回路のような8状態の順序回路を作るには、2進の記憶回路であるフリップフロップが最低3個は必要である。そして、3個のFFで構成する場合は実現可能な全ての状態を使うので、状態の割り当て方は(FFの名前は違っても、構造的に同じものは)一通りしか存在しない。

しかし、より多くのFFを使い取り得る状態の一部だけを使う設計も可能である。FFが多く必要になるので損をするように思われるが、状態の遷移に必要な回路(上図のFFより左側の回路)と出力に必要なデコーダ回路(上図のFFより右側の回路)が簡単になるように状態を割り当てると、全体としては少ない回路量で同じ機能が実現できる場合がある。

また、この例ではFF間の信号遅延は問題にならないが、より複雑な回路の場合は、うまい状態割り当てを考えることにより状態遷移やデコーダ回路が簡単になり、遅延時間の問題を緩和できるようなケースも存在する。

その一例として、8状態をFF1からFF8の8個のFFを使って表わす回路を次に述べる。8個のFFがあるので、全体としては2の8乗の256状態が表現可能であるが、FF1~8の状態を並べて表現すると、その中の(10000000)、(01000000)、(00100000)、(00010000)、(00001000)、(00000100)、(00000010)、(00000001)の8状態だけを使用する。この状態割り当ては"1"が1個だけでありそれを順次シフトして行くので、各FFの出力それぞれがA1、A2、A3、…に対応しておりデコーダは不要である。

遷移回路はSyncが"0"の場合にはFF1だけに"1"が入り、その他のFFには"0"が入るように構成する必要がある。そしてSyncが"1"になると、FF1の状態をFF2に、FF2の状態をFF3にというように順に上位側のFFにコピーをして行けば良い。この状態割り当てを行った8状態タイミング発生回路は次の図のようになる。

最初の回路ではFFは3個で良いが、ゲートは全部で25個必要となっている。一方、この回路構成ではFFは8個必要であるが、ゲートは16個で良い。また、次に述べるもう一つの例では4個のFFを使用し、(0000)、(1000)、(1100)、(1110)、(1111)、(0111)、(0011)、(0001)の8状態を使用する。

まず、Syncが"0"の場合は全FFの入力が"0"となるように遷移回路を作り、(0000)を作る。そして、Syncが"1"の状態では、クロックが入るとFF1はFF4の状態を反転し、FF2~4はそれぞれ前のFFの状態をコピーするように遷移回路を作れば、その他の状態を実現できる。この状態割り当てを行った回路を次の図に示す。各FFのD入力はNANDとインバータにより生成され、Syncが"0"の場合には"0"が入力され、Syncが"1"の場合には前段のFFの出力が入力となる。但し、FF4からFF1への接続だけは*Qから信号を取りフィードバックされるデータの極性を反転している。

出力のデコードは、A1状態は(0000)であり全FFの*Q信号をANDすれば良いが、全部の状態を使っていないので、実は、FF1とFF4が"0"の状態を検出すれば良い。そしてA2状態は(1000)であり、FF1が"1"、FF2が"0"であることを検出すれば良いので、FF1のQとFF2の*QのANDとなる。同様に、A3状態は(1100)であり、FF2のQとFF3の*QのANDとなる。この図ではその他の出力のデコーダは省略しているが、M1状態は(1110)であり、FF3のQとFF4の*QのANDである。そして、M2状態は(1111)はFF1とFF4のQのANDである。更に、X1状態は(0111)であるので、FF1の*QとFF2のQのAND、X2状態は(0011)でありFF2の*QとFF3のQのAND、X3状態は(0001)でありFF3の*QとFF4のQのANDで作ることが出来る。

従って、全体では4個のFFと16個のゲートで8状態のタイミング発生回路を作ることが出来、前述の8個のFFを用いる構成とゲート数は同じであるがFFは半分の4個と経済的である。また、最初の3個のFFを用いる回路と比較すると、FFは1個余計に必要であるがゲート数は9ゲート少なく、FFが何ゲート換算かにもよるが、一般に、より少ない回路量で実現可能である。また、ここではANDを作るためにNANDとインバータの2ゲートを用いたが、Sync信号をインバータで反転し、FFの反対側の出力とNORを取る方法でAND機能を実現すると各FFの遷移回路や出力デコーダはそれぞれ1ゲートで済むので、ゲート数カウントが変わってくる。

Faggin氏が4004のタイミング発生回路にどのような回路を用いたのかは本人に聞いてみないと分からないが、CMOSスタティック回路で作る場合は、ここで述べた3個のFFか4個のFFの回路例が適当であるが、4004を作ったPMOSダイナミック回路の場合は寄生容量で状態を記憶するためFFのコストが小さいので、構成が規則的で配置や配線の簡単な8個のFFの回路を用いた可能性もある。

なお、8個のFFを用いて"1"をシフトして8状態を作る回路はリングカウンタ(Ring Counter)、4個のFFを用いる回路(出力デコーダは含まない)はツイステッド(ねじれ)リングカウンタ(Twisted Ring Counter)と呼ばれている。