本連載はHisa Ando氏による連載「コンピュータアーキテクチャ」の初掲載(2005年9月20日掲載)から第72回(2007年3月31日掲載)までの原稿を再掲載したものとなります。第73回以降、最新のものにつきましては、コチラにて、ご確認ください。

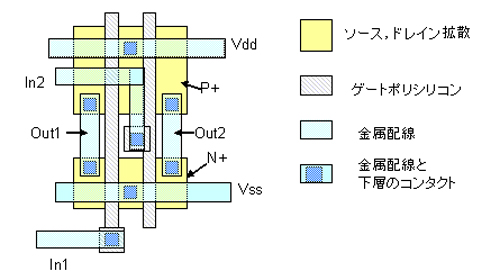

チップ面積は何で決まるかというと、当然、どのような回路がどれだけ載っているかに依存する。次の図は、前回掲載した2個のインバータのレイアウト図であるが、レイアウトルールを考えると、高さは14ピッチ程度、幅は5~6ピッチ程度となる。これは65nm半導体プロセスの場合、高さが2μm程度、幅が0.8μm程度であり、面積として1.6平方μmとなる。

つまり、最も小さいインバータ1個は0.8平方μm程度で作ることが出来る。2入力NANDはこのインバータ2個と同程度の大きさであり、3入力NANDでは若干大きくなる。平均として2平方μmで1論理回路(トランジスタのゲートと同じ言葉であり紛らわしいが、こちらもゲートと呼ばれる)が作れると考えると、論理回路だけを隙間無く敷き詰めると1平方mmに50万ゲートが収容できる。しかし、一般にはゲート間の配線が必要であり、これが制約となり、ゲートを敷き詰める場合に比べると1/3~1/4程度の密度の1平方mmあたり10万~15万ゲートとなる。この密度で500万ゲートのプロセサを作ると30~50平方mmとなる。

一方、メモリは特別にチューニングした最小寸法で高密度に作られ、1ビットのメモリセルは90nm世代で1平方μm程度、65nm世代では0.6平方μm程度である。これに歩留り向上のための冗長ビットやデコーダ、センスアンプなどの周辺回路が加わる結果、メモリの面積はビットセルの合計の面積の2倍程度になる。1Mバイトのキャッシュメモリは、パリティービットを加えて9Mビットであり、65nm世代でビットセルの面積が5.4平方mm、全体で10.8平方mm程度の面積となる。これをキャッシュメモリとする場合には、タグや制御回路が加わり15%程度大きくなり12.4平方mm程度となる。

ということで、500万ゲートのプロセサコアに4MBのキャッシュメモリを持つプロセサを65nm半導体プロセスで作ると、ゲート部分が30~50平方mm、キャッシュが50平方mmで、全体として90平方mmというデスクトップPC用プロセサとして平均的な面積となる。

しかし、これはかなり粗い見積もりであるので、どのくらいの精度があるのか実チップで検証をしてみよう。ISSCC 2006で発表されたIntelのサーバ用チップであるTulsaは、65nmプロセスを用い、2個のプロセサコアと16MBのL3キャッシュを搭載し、チップ面積は435平方mmである。

まず、キャッシュについて言うと、16MBのL3キャッシュのデータアレイがチップ全体の40%程度の186平方mmの面積を占めており、タグや制御回路を加えると214平方mmとなり1MBあたり13.4平方mmである。前述の見積もりの12.4平方mmより若干大きいが、実チップと良く一致している。

コアの面積は、内蔵している1MBのL2$を除くと、チップ全体の10%強の49.5平方mmである。ゲート数に関する情報は無いが、500万~700万ゲート程度と考えられる。また、各コアが1MBのL2$を持っており、これらがそれぞれ15平方mmあまりを占めている。これらを合計すると、以下のように343平方mmとなる。

- コア×2 : 99平方mm

- L2$×2 : 30平方mm

- L3$データ : 186平方mm

- L3$のタグ、制御回路 : 186平方mm×0.15=28平方mm

これでは、まだ、100平方mmあまりが残っている。その内の40平方mm程度が、何も無い空き領域と、プロセサの動作とは直接関係無い、多分、プロセスモニタなどに使われている。これらにどの程度の面積が必要となるかは、レイアウトの良し悪しにもよるが、Tulsaの例ではチップ全体の10%程度の面積であり、この比率より大幅に少なくすることは難しいと思わる。従って、チップ化するときのオーバヘッドとして10~20%を見積もって置く必要があると考えられる。残る60平方mmの内、20平方mm程度がFSBのI/Oバッファに使われている。一般的に、I/Oにどの程度の面積が必要となるかは、I/Oバッファの面積とチップ全体でのI/Oピン数に依存する。I/Oバッファの面積は、伝送速度は高速になると大きくなり、また、ドライバ、レシーバ単体か、両者を含んだトランシーバかによってもことなるが、別途、見積もって置く必要がある。

ここまで見てきて、更に40平方mm程度が残っているが、この部分は単に制御ロジックと書かれている。各コアのL2キャッシュから共通のL3キャッシュへのインタフェースやFSBへのインタフェースを司る部分である。デュアルコアのそれぞれのコアからのアクセスを調停し、データバッファなどを含んでいると考えられ、単純に面積換算でいうと400万から600万ゲート相当になるが、長い配線も多いと思われるので、400万ゲート以下であるかも知れない。この部分はデュアルコア化により肥大したと思われるが、ロジックのゲート数と配線を考慮したゲート密度から必要面積を見積もる必要がある。

以上のように、キャッシュとコアの面積の見積もりは比較的良い一致が得られるが、一方、実チップでは、I/Oバッファの面積、コアと共通キャッシュやFSBを接続する制御回路の面積を見積もり、追加する必要がある。そして、チップを作る上で避けられない空き領域などのオーバヘッドを10~20%見込むと、比較的良いチップ面積の見積もりが可能になる。