本連載はHisa Ando氏による連載「コンピュータアーキテクチャ」の初掲載(2005年9月20日掲載)から第72回(2007年3月31日掲載)までの原稿を再掲載したものとなります。第73回以降、最新のものにつきましては、コチラにて、ご確認ください。

MOESIプロトコルの説明で、書き込みにあたっては、他のプロセサの当該データを持つキャッシュラインをInvalid化したり、あるいは、Modifiedのキャッシュラインの物理アドレスへの読出し要求を送るとそのキャッシュラインを保持するプロセサが応答しデータを供給したりすると書いたが、このような動作を実現するためには、プロセサのキャッシュ間で緊密な通信が必要となる。

これを実現する方法として一番広く用いられている方法がブロードキャストとスヌーピングである。各プロセサは自分のキャッシュをミスした場合や書き込みを行うために他のプロセサのキャッシュラインのInvalid化を要求する場合には、読込み、書出し、データ送出、Invalid化要求などのコマンドとアドレスを全プロセサに放送(ブロードキャスト)する。そして、各プロセサは、この放送されるアクセス要求を常に監視し、放送されたアドレスでタグアレイを引いて、自分の持っているキャッシュラインが関係しているかどうかを常にチェックする。そして、他のプロセサからの読込み要求のアドレスが、自分のキャッシュラインに存在し、データ供給責任がある場合は、要求に応じてキャッシュラインのデータを送り出し、また、状態がModifiedであればOwnedに変更するなどの状態遷移を行う。また、Invalid化要求のアドレスが自分が保持しているキャッシュラインと一致している場合は、そのキャッシュラインをInvalid状態とし、要求された処理を行ったという応答を返す。

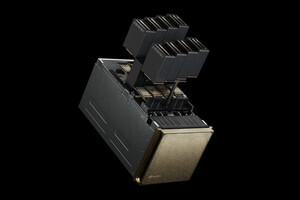

IntelのXeon MPのように電気的なコモンバスで接続されている場合は、コマンドとデータをバスに載せれば全部のプロセサが見ることができるが、AMDのOpteronの場合にはHyperTransportを通じてパケットとしてプロセサ間を順に送る必要がある。

Opteronはメモリコントローラをチップに内蔵しているので、自分のメモリにデータがある場合は他のプロセサとは無関係にメモリにアクセスできると思っている人が多いようであるが、キャッシュコヒーレンシを維持するためには、メモリアクセスを行う場合は全てのプロセサにコマンドとアドレスを送り、他のプロセサがModified状態のキャッシュラインを持っていないかどうかを確認するため、上記のようなステップを踏む必要がある。それでもOpteronのメモリアクセスが速いのは、4個のプロセサをリング状につないだ4ソケットシステムでは、順に送ると言っても最長でも距離は2で、中間のプロセサによる中継は1回しかないのであまり遅延が入らないことと、プロセサ数が増えるに従ってDRAMメモリへの総バンド幅が比例して増えるという点が大きく貢献している。

一方、Xeon MPの場合はプロセサ間は直結であり距離1であるが、コモンバスであるので電気的なスピードが遅いことと、一つのFSBを全プロセサで共用するので、プロセサ数が増えてもメモリバンド幅は一定で増加しないという点でOpteronに対して苦戦している。

このようなアドレスをブロードキャストし、各プロセサはそれをスヌープする方式は、システム全体で見ると要求の数はプロセサの個数に比例して増加する。従って、プロセサ数が増えると各プロセサが単位時間に処理するスヌープ数もそれに比例して増加しないと、スヌープが処理性能のボトルネックとなってしまう。大規模サーバを作る各社はこの部分に工夫を凝らし32CPU程度まではスヌープ方式で実現しており、富士通のPRIMEPOWER 2500では128CPUと世界最大のスヌープ方式のサーバを実現しているが、これ以上の大型化は難しい状況である。

これに対して、各プロセサが自分のメモリの内容をどのプロセサのキャッシュに送ったかを記憶するディレクトリを持ち、ブロードキャストではなく関係するプロセサだけに要求を送る方式がディレクトリベースのccNUMA(cache coherent Non Uniform Memory Access)という方式であり、SGIのAltix 3700はこの方式で512CPUのシステムを実用化している。しかし、ccNUMAの詳細についてはここでは割愛する。