CXL

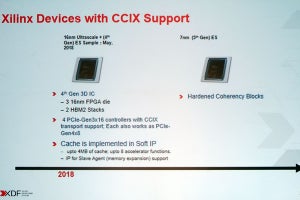

というわけで、CCIXはOpenCAPIやGen-Zとそれなりに棲み分けをしつつ、普及に向けて進んでおり、すでに昨年からXilinxのFPGAには実装されて出荷されている。

今年はAMDのRADEON Instinct MI50/60がすでにPCIe Gen4/CCIXに正式にサポートを謳っており、今年第3四半期にはRomeベースのEPYCも出荷され、これでHostとAcceleratorの両方がCCIX対応となる訳だが、ここにいきなりCXL(Computer Express Link)なる「CCIXとよく似た別のモノ」をブッ込んできたのがIntelである。

今年3月11日、いきなりCXL Consortiumの設立を発表した。設立メンバーはAlibaba/Cisco/Dell EMC/Facebook/Google/Hewlett Packard Enterprise/Huawei/Intel/Microsoftという、先ほどのPhoto13と見比べてみると異様なほどにシステムベンダーばかりとなっている。

もっとはっきり書いてしまえば、この中でAcceleratorとかHostとかを作るベンダーは皆無で、いずれもIntelの標準品(Cisco/Dell EMC/Hewlett Packard Enterprise/Huawei/Microsoft)ないしカスタム(Alibaba/Facebook/Google)のXeonを使ってシステムを構築しているベンダーばかりである。さすがに現時点ではメンバー企業も大分増えたが、Promotorは前述の9社のみ。残りはContributorもしくはAdaptorとなるが、何社がContributorで何社がAdaptorなのかはCXLのページでは判明しない。

CXL ConsortiumがCCIXとかGen-Zと根本的に異なるのは、Consortium設立時にすでにSpecification 1.0が完成していることだ。要するにIntelは社内でCXLの仕様を完成させて(もっと正確に言えば、CXLの元仕様を完成させたうえで、それをOpen化することを決めて)から、おもむろにCXL Consortiumを立ち上げたという形になる。Open Standardを立ち上げるやり方としては(そうした前例は無くはないが)あまり一般的な方法とは言いにくい。

ただこれに続くSpecification 2.0については、PromotorおよびContributerの中からTechnical Working Groupのメンバーを募り、ここで策定作業をするという話になっているので、一応Open Standardとしても問題ではないだろう。このやり方のメリットは、圧倒的な時間の短縮である。CCIXの場合、Consortium結成からSpecification 1.0の公開までほぼ2年近くを要している。だからCXLで同じやり方をしようと思ったら、Specificationの完成が2021年位になりかねないが、これはCCIXに対して致命的な遅れである。多少乱暴でも、とにかく早く仕様を策定する必要があった、という事だろう。

もう1つ事情を書いておけば、ALCFに納入されるAuroraではCXLとOne APIを利用してアプリケーションのインフラを構築することが明らかにされている。これに間に合うようにハードウェアを構築するためには、もう現時点でSpecificationが固まってないと、いくら何でも実装は難しい。恐らくこのあたりは2017年のSC17でKnights Hillをキャンセルした(& Raja Koduri氏がIntelに入社した)あたりから、検討を始めたのだと思われる。

Knights Hillを利用する最初のAuroraのプランではIntelのOmni Fabricを利用して接続という話だったが、そのKnights Hillのキャンセルに加えてOmni Fabric自身の問題もあったらしい。そうなるとAurora改では別のAccelerator向けI/Fが必要になる。最初の"Before CCIX"のところで説明したように、CPUソケットにFPGAを無理やり突っ込むようなソリューションはサーバ機には難しいし、かといってカードエッジタイプのUPIを開発するというのも無茶である。なによりUPIはIntelの独自バスで、仕様は公開されていない。CCIXに対抗するためにはOpen Standardでないと難しいし、だからといってUPIをOpen Standard化するという訳にもいかない。CXLを新たに開発する事そのものは必須だったと言っても良い。

実はこの辺りを忍ばせる記述はSpecificationに溢れている。後で出てくるPhoto26を見ると、Requestが"Intel AL.$"/"Intel AL.mem"/"Intel AL.io"と記されている。で、Specificationの最初の"Terminology / Acronyms"の注意書きで"Intel AL"は"CXL"と読み替えろとされている。このIntel ALというのはIntel Accelerator Linkの略で、要するにそういう独自規格を開発しており、これをOpen化する際に名前をCXLに変えた、という事だと思われる。

余談であるが、代理店経由で「なんでCCIXを使わなかったのか? もしくは、CCIXの何が問題だったのか?」という質問を一応CXL Consortiumには投げてみたところ、以下のような返事を頂いた。

"The industry needs open standards that can comprehensively address interconnect challenges in the new era of artificial intelligence, machine learning, cloud, and more - and there can be more than one option. CXL is an example of the industry forming a new open-standards framework. The market and individual companies will decide the right approach for their applications.

From a technology standpoint, CXL is defined to be lightweight on the device side. Coherency is implemented on the CPU side, making it simpler for the device side to implement CXL. We are also leveraging PCIe infrastructure for performance."

CCIXについての言及が無いのはまぁこの手の回答としては当然であるが、Intelとしては、すでに自分で作った規格があるので、他社が作ったStandardに乗る必要性を感じなかったのだろう。もともとOpen Standardのメリットは、その仕様策定に当初から参画することで先行者利益を享受するところにある。ところがIntelはCCIXの仕様策定に一切絡んでおらず、その意味でもCCIXを採用するメリットは(Intelには)無い、と判断したのだと思われる。

加えて言えば、後半の"lightwight"がCCIXとの大きな違いと言える。特に、"Coherency is implemented on the CPU side"が最大のポイントという事になるのだろう。Intelからすれば、完全なキャッシュコヒーレンシは必要なく、あくまでCPU側だけでキャッシュコヒーレンシを管理するような仕組みで十分(CCIXの様に、それこそノード間接続に使ったりするつもりは一切ない。そのためにはUPIがすでにある)と判断したと考えられる。

話を戻すとこのCXL、当初は一切資料がなく、4月に入ってからやっと3PのWhite Paperがリリースされた。次いで4月中旬には、Specificationまでダウンロード可能になった。CCIXの場合、メンバーにならないとSpecificationが入手できないので、この点に関してはCXLの方がより優しい(?)対応になっている。

さてそのCXLであるが、構成の概略をまとめておこう。CXLはPCI Express Gen5と共存する形になっている(Photo23)。

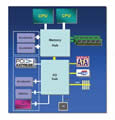

Photo24は内部の概略図であるが、CXL.cache、CXL.memory、CXL.ioという3種類のCXLプロトコルが新たに定義される。

ここで、

- CXL.cache:単純な要求/応答プロトコルを使用利用して、CXL DeviceはHost MemoryからデータをCache可能。HostはSnoop Messageを利用して、Device側のCacheのCoherencyを管理する。

- CXL.memory:HostからCXL Device側のLocal Memoryをアクセスする手段。CXL.memoryのTransactionは、単純なMemory Load/Storeのみを管理する。この際のCoherencyもHost側の処理となる。

- CXL.io:PCI ExpressベースのI/O Protocolで、Device Discovery, Initialization, I/O Virtualization, DMAなどが提供される。CXL.ioは当然ながらCache Coherencyが提供されないし、アクセスできるのはI/O空間のみである。CXL.ioに関しては、基本的にはPCI Express用のソフトウェアがそのまま再利用可能になる事を目指すが、CXL.cacheやCXL.memoryとの兼ね合いもあって若干の機能追加が必要になる。

といった形である。

もう少しだけ、Specificationから内部構造をご紹介したい。まずは階層構造(Photo25)。

Photo02と比較していただくと判るが、CXLでは基本的にはPoint to Pointの接続しか考えていないようで、なのでLink LayerがPCIeとCXLで並列になっているのが大きな違いである。またCXL Version 1.0では以下の3つのTypeのCXL Deviceが想定されている(Photo26)。

- Type 1:Host MemoryをCache Coherencyでアクセスする必要があるが、Local Memoryは持たない(or Local MemoryはHostからはアクセスできない)タイプ。FPGAで、外部メモリは持たない(ローカルメモリは全部Working Memoryとして使い、Hostのメモリ空間にはMappingしない)ようなケースがこれに相当するだろう。

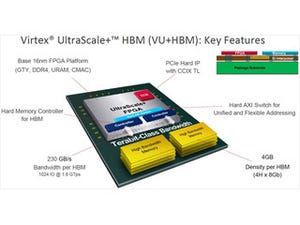

- Type 2:CXL Device側も大容量かつ高速なメモリ(例えばHBM2)を搭載する場合がこれになる。Type 1との違いは、そんな訳でCXL DeviceをアクセスするためのCXL.memoryのアクセスが追加されていることだ。

- Type 3:Memory Expander。これはおそらくOptaneを使った大容量のメモリを想定しているものと思われる。この場合Cacheは必要ないので、CXL.cacheのやり取りはなくなる形だ。CXL.ioのLinkが残っているのは、同期を取るとか管理を行うといった要件のためと思われる。

細かな詳細は今回は省くが、Agent周りの実装がCCIXと比べるとかなりシンプル(例えばCCIXの場合、Request Agent/Home Agent/Slave Agentの数は定められていない(実装依存:多いほど同時に扱えるトランザクション数が増えるが、その分コントローラの実装が複雑になるのでトレードオフとなる)が、CXLだと例えばCXL.cacheを扱うのは3chと規定されているなど、割とシンプルである。その意味では、性格というか位置付け的にはCXLはCCIXというよりはOpenCAPIに近い。ただそれをPCI ExpressベースにしたところがCCIXに近い訳で、そんな訳でOpenCAPIとCCIXの丁度中間あたりにCXLは位置付けられる事になる。

要はFPGAとGPGPU(Intel Xe)、それとOptane Memoryをつなぐ事しか考えていないのが現状という訳だ。もちろんこのあたり、今後CXL Version 2.0の仕様策定作業の中で性格が変わっていく可能性はある。

また、技術的に見れば、これもFPGAなどを使ってCCIX/CXL Bridgeを作る事は不可能ではない様に思われる。そのニーズがどこまであるのか、と言う部分は読めない。

ということでCCIXとCXLを中心に簡単にご紹介させていただいた。一言でまとめれば「よく似た別のもの」であって、ターゲットはPrimaryがGPGPUとFPGAベースのAccelerator、CCIXではSecondaryがSoC間の接続などになるだろう。恐らく2つの規格はお互い相容れないまま、それぞれ展開されていくことになる。大昔のVHSベータ戦争みたいなものだ。もちろん現在のInstall Baseで数えればXeonの方が圧倒的に多い訳であるが、CXLが利用できるのはIntelの「将来の」Xeonプラットフォームに限られることになる。現実問題としてCXLのプラットフォームが登場するのは早くて2020年末、普及するのは2021年以降になる(Ice Lake-SPはPCI Express Gen4なので、CXLが利用できない。つまりIce Lake-SPの次になる)。そんなわけで、勝負が始まるまで今しばらくお待ちいただきたい。