CXL

Memory Controllerのついでに、CXLについても触れておきたい。CXLはAccelerator及びAttached Memory向けのI/Fなので、別にAttached Memory専用という訳では無い。しかしながら、IntelがOptane Memoryのビジネスを収束させることを発表し、かつ3rd PartyのNVDIMMが不発というか全然盛り上がっていない現状で、大きく期待されているのがCXLを利用したAttached Memoryであるのは事実である。実際MicronはOptaneというか3D XPointのビジネスから撤退を発表した際のリリースの中で"Micron sees immense promise in new classes of memory-centric solutions that utilize CXL to scale the capacity, performance and content required by applications to run on infrastructure with greater architectural freedom."(Micronは、CXLを利用することで、アプリケーションに必要な容量、性能、コンテンツを拡張し、アーキテクチャの自由度が高いインフラストラクチャで実行する、新しいクラスのメモリ中心のソリューションに大きな可能性を見出している)と明言しており、非常に積極的である。

そもそもIn-Memory ComputingはこれまでIntelのOptane Persistent Memoryを中心にソフトウェアが開発されてきたこともあって、現状はXeonの独壇場である。ところがそのOptane Persistent Memoryそのものの先行きが無くなってしまった。とりあえずSapphire Rapids向けにはCrow Passとして開発されてきたOptane Persistent Memory 300シリーズがリリースされたが、こちらは容量512GB。Xeonの場合は8chのDIMMにこのOptane Persistent Memoryと通常のRDIMMを1枚づつ装着することで、chあたり768GB。8ch合計で6TBの容量が確保できるとしているが、Genoaはそもそも12chに2枚づつ256GB DIMMを装着すれば6TB容量になるわけで、もはやOptane Persistent Memoryのメリットは半減している(不揮発性、という部分に多少のメリットが残される程度)。しかもCXLで利用可能なSwitchを利用したMemory Poolみたいな事はOptane Persistent Memoryには不可能である。なのでこれまでOptane Persistent Memoryを前提に構築されていたIn-Memory Computing Applicationは、現在CXLベースへの移行作業を始めていると思われるが、これには相応の時間が掛かる。Optane Persistent Memory 300シリーズは、このアプリケーションの移行作業が完了するまでの間、既存のアプリケーションを使える様にするために提供されていると考えれば良いだろう。

さてそんなCXLであるが、AMDは割と意欲的であり、Genoaは、CXL 1.1+の機能が実装されている(Photo24)。"+"って何だ? という話だが、GenoaはCXL 1.1に完全準拠した上で、CXL 2.0の一部の機能を先行して実装している。具体的にはCXL 2.0で追加されたRAS機能及びPersistent Memoryのサポートである。2.0で追加されたその他の機能、具体的にはCXL SwitchingとかMemory Pooling、Hot plug、QoS telemetry、eFLRなどの機能はまだ未実装である。もっともMemory PoolingとかSwitchはCPU側が対応しただけでは駄目で、SwitchやらPool用のApplianceの開発も必要になるから、現状はまだ時期尚早というのは判る。それよりもRAS機能とPersistent Memoryのサポートが早くも追加されたことで、DRAMだけでなくNAND FlashベースのSSDも接続が可能になったという事は大きい。先ほどPhysical Addressが52bitになった話の説明の中で、16TBのNAND SSDベースCXL Memoryを引き合いに出したが、実際にGenoaでは技術的にはこれが可能にである(Sapphire Rapidsは今のところDRAMベースのMemoryしかサポートしていない)。

-

Photo24: 一瞬CXLのType 1/2のサポートが無いように読めてしまうが、そうではなくCXL 1.1準拠のType 1/2/3のサポートがあり、これに加えてCXL 2.0 Type 3のサポートが追加されているという意味である。

もう一つ、Sapphire RapidsがサポートしておらずGenoaがサポートしている機能に、Lane Bifurcationがある。Photo16で、1つのGenoaのSocketからは4本のCXL Linkが出ているのが判るかと思うが、各々のLaneはx16になっている。Sapphire Rapidsも同じくx16構成のCXL Laneを4つ利用可能であり、対応するDeviceは4つである。例えばx4構成のCXL Memoryを装着した場合、残りのx12 Laneには何も装着できなくなる。これに対してGenoaの場合、x16 Laneをx8 Lane×2、あるいはx4 Lane×4に分割して、それぞれ別のCXL Memoryを接続する事が可能になっている。なので、x4 Lane Memoryなら最大16個装着できる格好だ。

ちなみにこの分割したLaneはInterleaveも可能になっている。x8 Lane×2の場合は64Bytes Boundaryで、x4 Lane×4の場合は256Bytes BoundaryでInterleaveが行われる格好だ。更に言えば、4つのCXL Link同士でも2-wayないし4-wayのInterleaveが可能であり、全体を一つのCXL Memoryブロックとして扱う事も出来るようになっている。

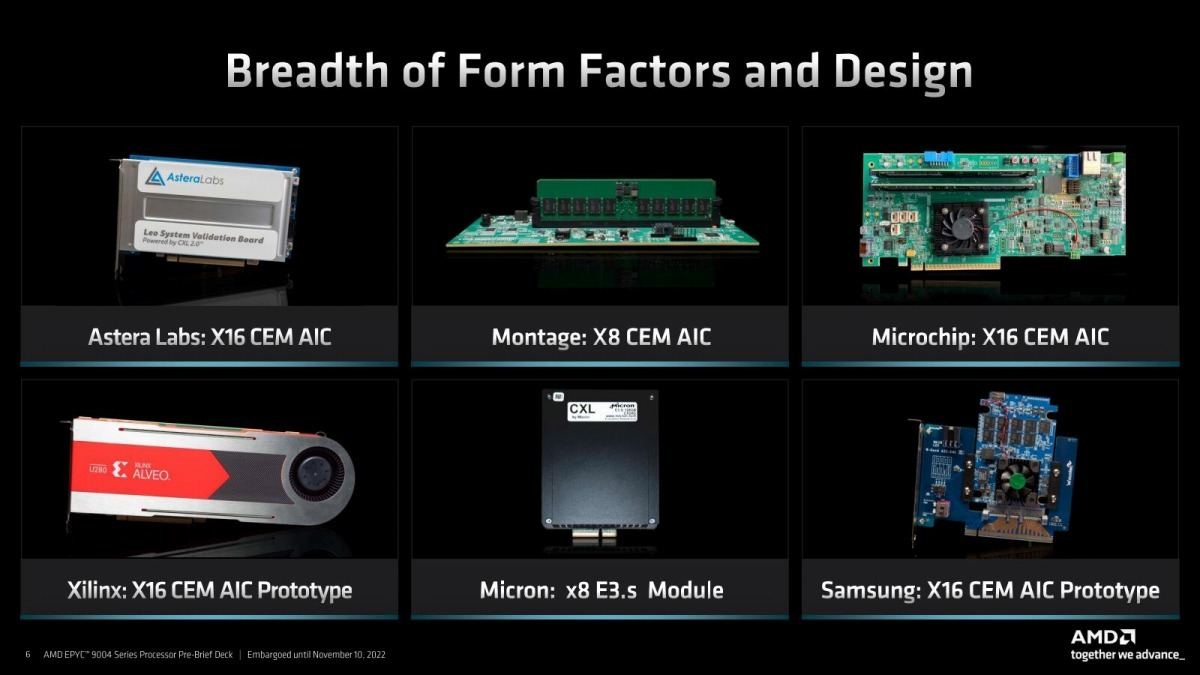

一方、これに装着できるCXL Deviceの方は? というと、昨年5月にSamsungは512GB CXL DRAMのサンプル出荷を発表している(Photo25)し、Genoaの発表にあたっては多くのベンダーのプロトタイプが示された(Photo26)。

Astera Labs(Photo27,28)は実際にCXLの先にそれぞれ2chのDDR5 DIMMを装着して、ローカルのDDR5-4800と性能差が無い事をアピールした。実際PCIe Gen5 x16だからレーンの帯域は64GB/secになり、DDR5-4800の2ch(76.8GB/sec)にはやや届かない計算になるが、実際にはそこまでの帯域を使い切れないというのは先のStreamのベンチマークでも示された通り。Photo28の結果はnumactlを使ってベンチマークを行った場合のもので、別のNUMAノードとしてCXL経由でDDR5を利用できるとしている。

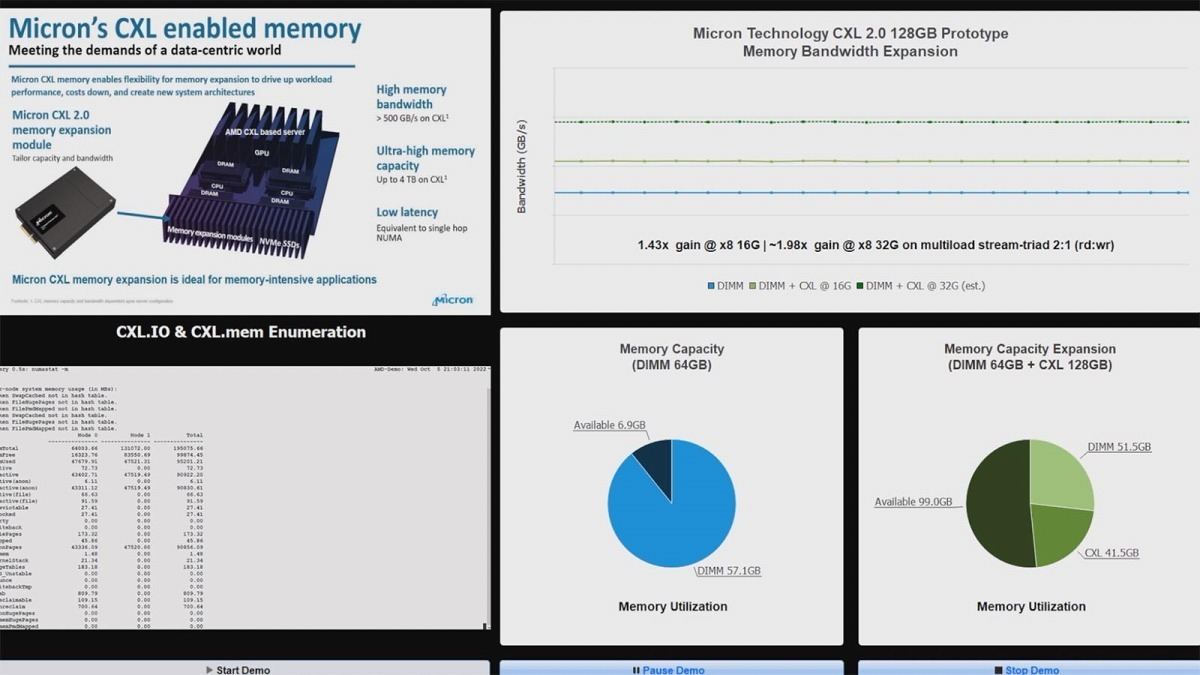

MicronはE3.sモジュールを通常のDIMMと混載する形で動作させ、帯域が1.43倍(PCIe Gen4)~2倍(PCIe Gen5)に増えるというLive Demoを披露した(Photo29)。

-

Photo25: このデバイスそのものは2021年に発表されているのだが、I/Fがx8からx4になった。

-

Photo26: 左下のXilinxのAlveoも含めて全てCXL Memoryのプロトタイプ。AlveoはU280と書いてあるが、実際にはVersal Primeあたりを搭載してCXLのプロトコルをProgrammable Logicで実装した未発表品ではないかと思う。

-

Photo29: 右上が実際のBenchmarkの結果。水色(DIMMのみ)と緑(DIMM+E.3s)が実測値。現在はプロトタイプでPCIe Gen4(16G)の速度で接続されているためで、32G(Gen5)になると帯域が2倍になる、としている。

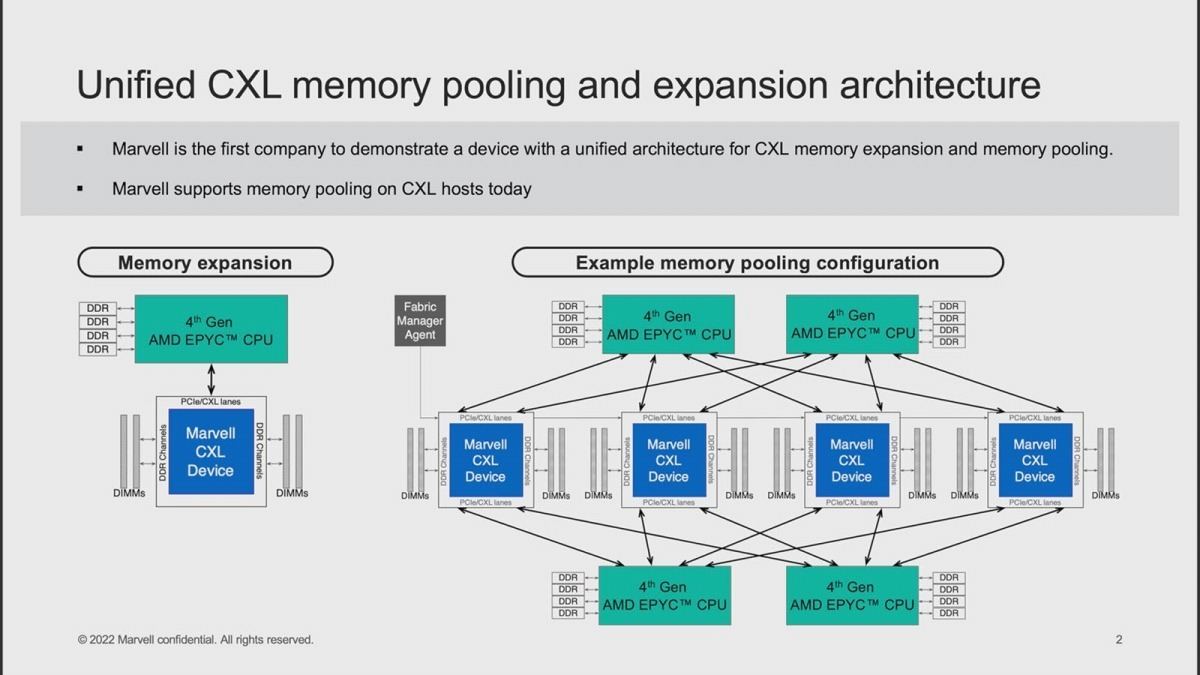

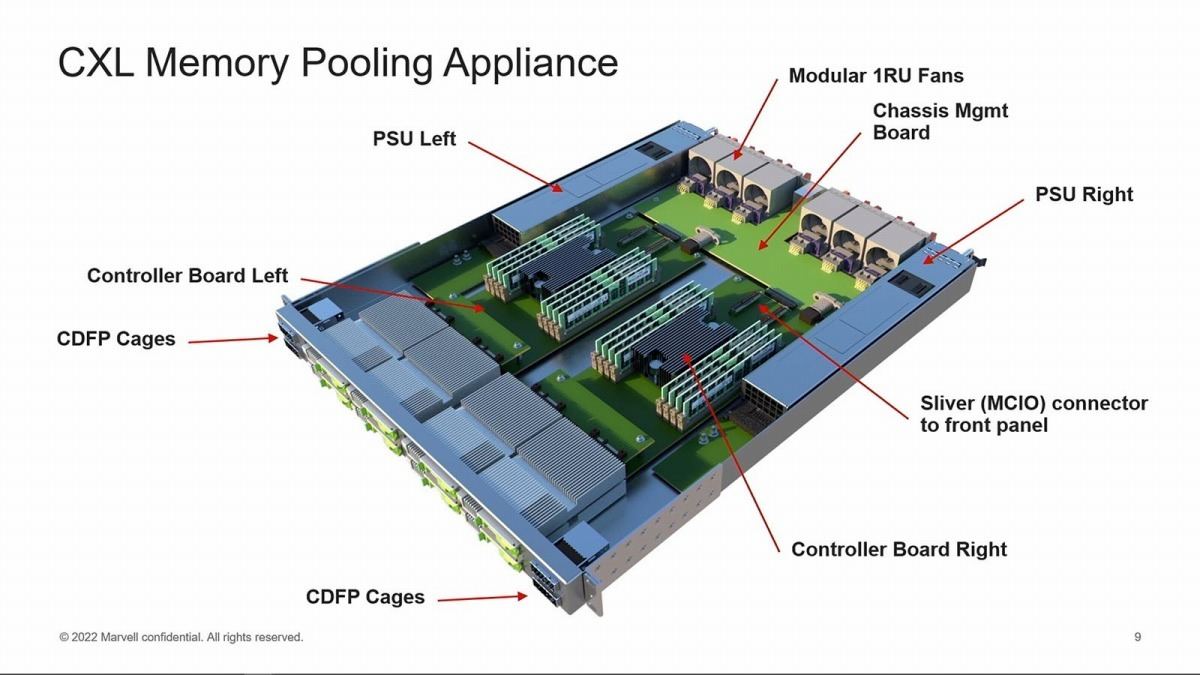

もう少し凝ったLive Demoを披露したのはMicronである。先に書いたように現状のGenoaではまだMemory Poolingには未対応であるが、MarvellはこれをMemory Appliance側に実装する事で実質的にSwitchとMemory Poolを実現するという構成である(Photo30)。このMemory ApplianceはほぼEPYCの2Uサーバーと同じ程度のサイズである(Photo31)。これ一つで6つのMemory Deviceを構築できる予定らしいが、内部構造(Photo32)を見ていると2 Deviceにしか思えないあたりがちょっと謎である。Photo31は現在のテストシステムの構成、Photo32は将来の予定構成なのかもしれない。実際に、Marvellの提供するソフトウェアを利用してMemory Poolingが行える様子も示された(Photo33)。

-

Photo32: このController Boardは、EPYCではなく恐らくはMarvellの自社SoCと思われる。OCTEON 10 DPUあたりだろうか? CDFSはPCIe Cable用のコネクタで、ケーブル経由でCXLの接続を行うものと思われる。

-

Photo33: 今はAd-Hocな形の実装の様で、今すぐ広範に利用できるという訳では無いが、GenoaベースでMemory Poolを技術的には利用できる事を示したという意味では意味のあるデモである。

CXLのエコシステムは、やっと商用プラットフォームが立ち上がったという段階なので、次にOSやミドルウェア、アプリケーションのベンダーがこれに対応するフェーズに入った訳で、CXLベースのIn-Memory Computingが本格的に立ち上がるのは2024~2025年辺りになりそうではあるが、ただそうしたCXLの立ち上がりを牽引してゆくのはGenoaという事になるだろう。

勿論CXLのエコシステムはIntelを無視する訳では無いだろう。Sapphire Rapidsは、公式にはType 3(つまりCXL Memory Expansion)は未サポートであるが、プロトコルとしてはCXL.io/CXL.mem/CXL.cacheの3つを完全にサポートしており、Type 3に関しては「技術的には動作するが、検証プラットフォームが無い関係でValidationを行っていないので、サポートを表明していない」という扱いである。なので現実問題としては動作するだろうし、エコシステムでも対応や検証を行ってゆくだろうとは思うが、先に書いたようにRAS機能とかPersistent Memoryは今のところGenoaのみのサポートだし、Lane Bifurcationのサポートも無いので、ちょっと使い勝手は悪いだろう。なによりOptane Persistent Memory 300をサポートしている間は、公式にもCXL Memory Deviceをサポートするとは表明しにくいと考えられる。そうした意味でも、現状ではGenoaを利用してアプリケーションのCXL Memory対応を進めるのが賢明と考えられる。