MCCのダイサイズ

今回、XCC用と思われるWaferが公開された(Photo08)が、300mmウェハで縦横15個分ずつであり、Tileのサイズはほぼ20mm×20mm。事前情報では400平方mmとされていたが、この数字がほぼ正しい事が改めて確認できた格好だ。

さて、Photo09はその拡大図である。

赤/黄/青は筆者が追加したものだが、多分こういう比率で問題ないと思う。さて、この想定だとするとCore+LCCのサイズ(+内部のRing Bus)の寸法は4×4構成で13.6mm×15.6mmといったところ。つまりBlock 1つ分のサイズは概ね3.4mm×3.9mmで13.26平方mmと結構大きい。Interface部の寸法もおなじである。ということで図1に出てくる20Block分の寸法は17.0mm×15.5mmほど。残った周辺部はAcceleratorとかEMIB接続用のI/Fということになる。この周辺部の面積は合計で136.5平方mmになるので、確かにAcceleratorを搭載するには十分なサイズである。

さて、ここからMCCのダイサイズを推定してみたいと思う。Photo07にあるように、MCCコアは7×7の49個のBlockから構成される。ここに今の寸法を当てはめると27.3mm×23.8mmで、49 Blockでほぼ650平方mmに達する計算だ。ここにAccelerator用の面積を例えば100平方mmほど充てたとして、Tile全体の合計のサイズは750平方mmに達する計算になる。今回発表された中で一番安い製品は8coreのXeon Bronze 3408UでRCP(Recommended Customer Price:推奨小売価格)はたったの415ドルなのだが、これ、原価割れしてないかちょっと心配になってくるダイサイズである。もっとも今回発表の52製品のうち、RCPが1000ドルを切ってる製品は4つしかないので、トータルとしてはそれほど問題ではないのかもしれない。

しかしこうなると、トータルでこそ1600平方mmと巨大ながら、Tileあたりで言えば400平方mmでしかないXCCと、本当にMonolithicで750平方mmの巨大なMCC、どちらの方がYieldが高いのだろうか? とちょっと心配になってくる。

ArchitectureとCXL

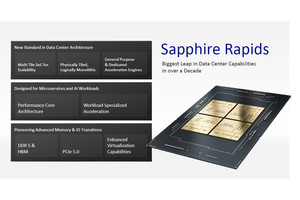

ところでSapphire Rapidsそのもので言えば、CPU CoreはAlder Lakeと同じGolden Coveベースである。Golden Coveそのものではないのは、L2/L3の容量が異なる(Photo10)事と、あとはAMXに対応している事だ。

ただAMX命令に関してはCPU側のDecoderで解釈される訳ではなく、AMX側で処理されるためにDecoder部には手は入っておらず、違いはCPUIDにAMX対応を示すbitが追加された程度である。

Golden Coveのコアの性能そのものは以前こちらで評価しており、動作周波数の違いとかはあるにしても基本的な特性は変わらない。変化があるとするとメモリコントローラ周りであろうか。

そのメモリコントローラ周りであるが、こちらでも触れた様に今回第4世代Xeonスケーラブル・プロセッサに合わせてOptane Persistent Memory 300シリーズが投入される事が明らかになっており(Photo11)、当然Alder Lakeとは別物になっている。

-

Photo11:Optane Persistent Memory利用時はDDR5-4400が上限になる模様。ただその分1chに2 DIMMまで行けるので、トータルで16枚/Socketの装着が可能になる

Optane Persistent Memoryの容量は最大512MBということで、2 Socketだとトータル32枚で16TBが狙えるか、と思ったらSocketあたり4TB、2 Socket構成で合計6TBに制限されているのは、恐らく既存のOptane Persistent Memory 100/200シリーズとのソフトウェア(主にOSとかミドルウェア)の互換性を保つためと思われる。

ところで恐らくこのOptane Persistent Memoryのあおりを喰らったと思われるのがCXL Memoryのサポートである(Photo12)。

-

Photo12:ちなみにCXLはSocketあたり4つまでとなっている。CXL Memoryは現在リリースされているのが大体x8だから、PCIe 5.0の80LaneのうちCXLに32Lane、残りがの48LaneがNetworkなど向けやNVMe SSD向けなどという格好だろうか?

今回公式に、CXL 1.1のType 1およびType 2をサポートすると表明された一方、Type 3のサポートが無い。ただ以前こちらで説明した様に

必要なプロトコル

- Type 1: CXL.io CXL.cache

- Type 2: CXL.io CXL.cache CXL.mem

- Type 3: CXL.io CXL.mem

であって、Type 2がサポートされているのにType 3がサポート出来ない技術的な理由がない事になる。これについて直接聞いたところ「技術的には(Type 3も)動くが、我々はそれを検証するためのプラットフォーム(要するにCXL Memory Device)を持っていないのでサポートから外した」という返事が戻ってきた。つまり挿せば多分動くのである。それに、ここでも説明したが、すでにSamsungは2022年5月に製品をリリース、SK HynixやMicronも製品や評価サンプルをリリースしている状況でこれはちょっと無理がある。要するにCXL Memoryに公式対応してしまうと、Optane Persistent Memory 300シリーズと思いっきり被るため、敢えて今は未サポートとしたという辺りが正直なところと思われる。多分これが正式にサポートされるのは、次のEmerald Rapid世代になるかと思われる。