既報のとおり、米国時間の2023年1月10日、Intelは第4世代Xeonスケーラブル・プロセッサおよびXeon Maxの発表会を開催した。これを踏まえて、もう少し細かい話をご紹介したいと思う。

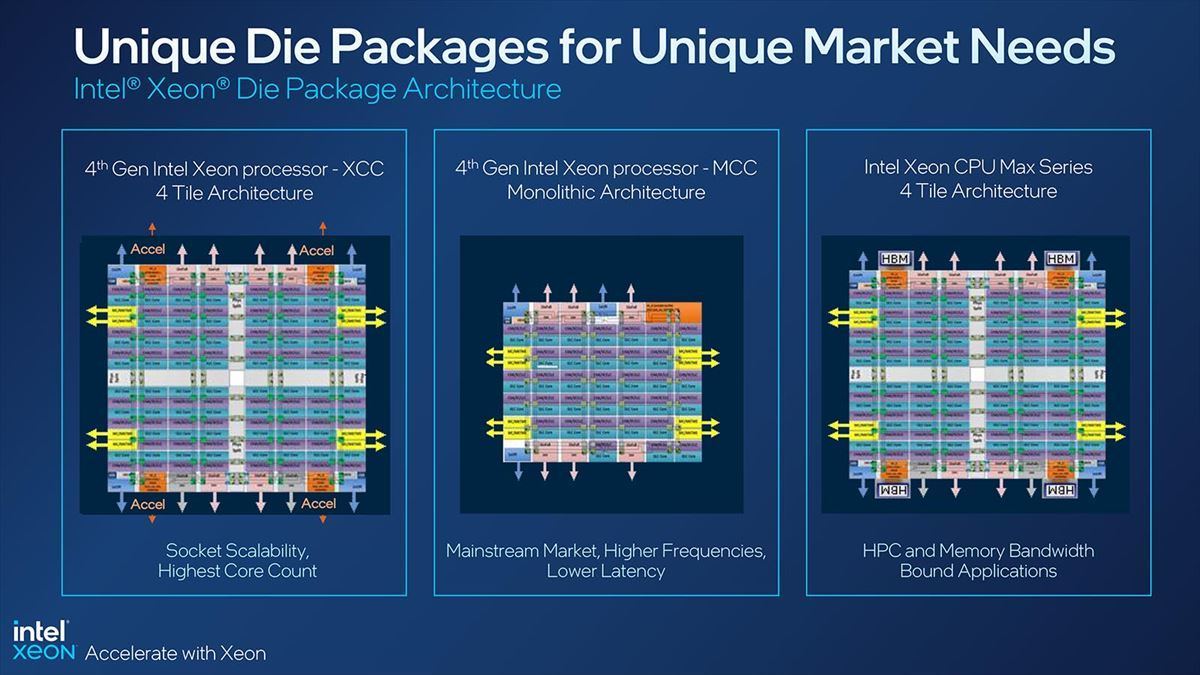

ダイは3種類

すでに説明した様に、第4世代Xeonスケーラブル・プロセッサ/Xeon Maxでは、

- MCC:最大32core

- XCC:最大15coreのダイ×4のMCM

- HBM:最大14coreのダイ×4+HBM2e×4のMCM

の3種類のラインナップがある。

32coreまでの製品は全てMCCで、34core以上は全てXCCかHBMになる。厳密にいうと、Xeon Maxのローエンド(Xeon 9462)は32coreなのだが、MCCにはHBM I/Fを持つダイがないので、こちらはHBMでの実装となるが、後は全部MCCだ。製品ラインナップを見ると、32core以下はXeon Gold/Silver/Bronzeの扱いになっている(Xeon Maxは32coreでもXeon Max扱い)ので、区別としてはGold/Silver/BronzeがMCC、PlatinumがXCC、MaxがHBMと考える方が実情に合っていると言える。

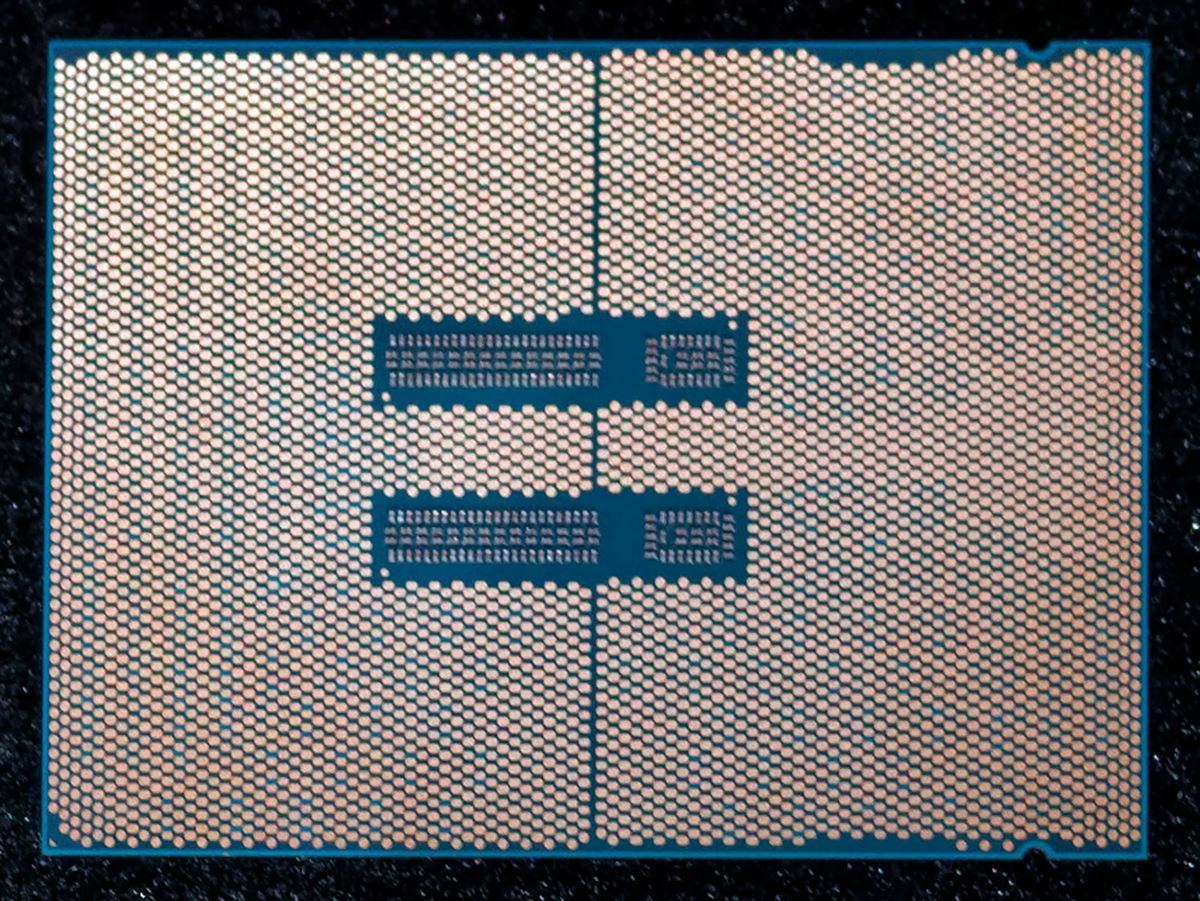

さて今回発表会でも事前説明会でもMCCのダイは公開されておらず、示されたのはXCCとHBMのみである(Photo01)。

XCCの方は事前に説明されていた通りの構造(Photo02,03)である。

一方HBMであるが、こちらはHBM2eをStackする関係で、パッケージの両横に耳が追加されており、追加のパスコンやFPGAが追い出されているのが判る(Photo04,05)。

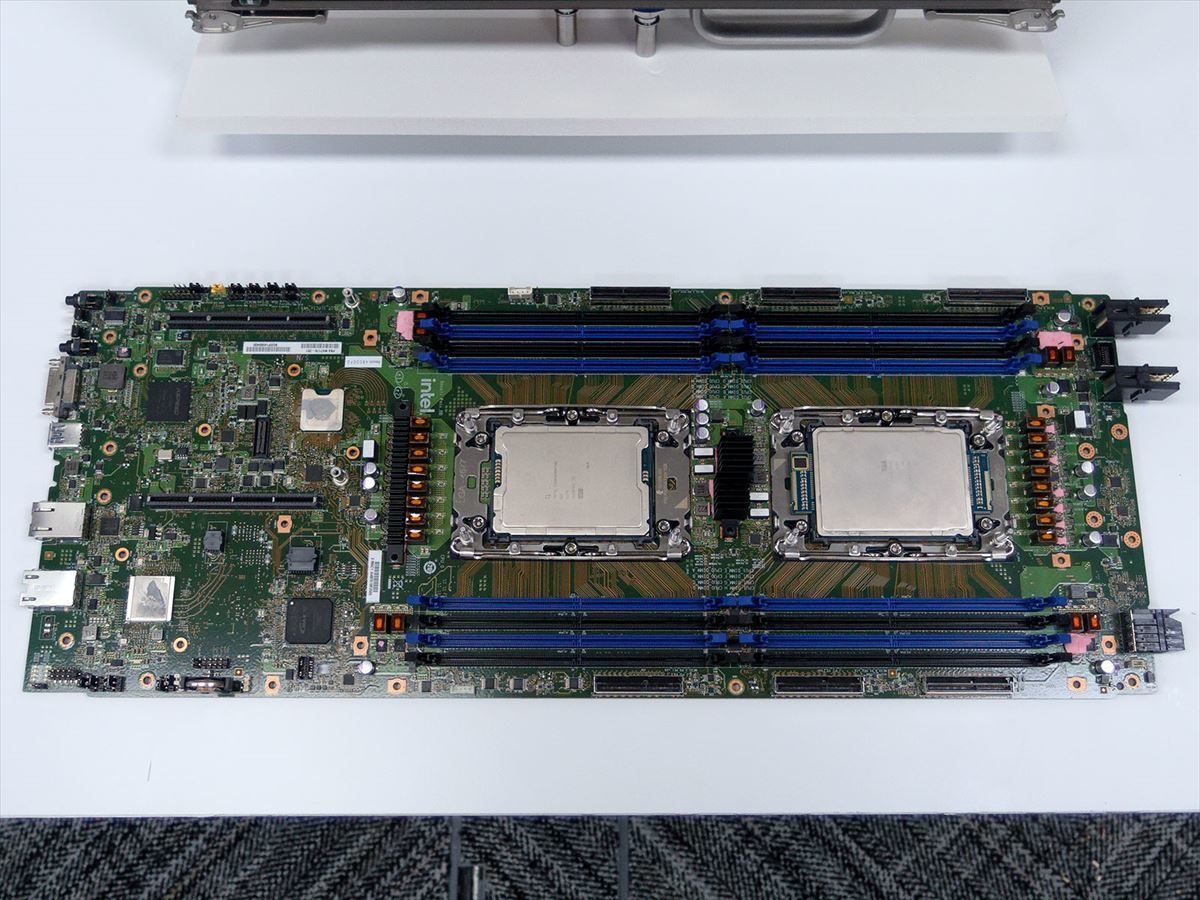

面白いのは、XCC(やMCC)とHBMはSocket互換な事だ。実際事前説明会では、両方が同じSocketに収まる事をデモしていた(Photo06)。

さて、次にそのXCC/HBMの構造であるが、ちょっと筆者の想像を超える代物だった。XCCあるいはHBMの場合、4つのTileをEMIBで相互接続するという仕組みになっている事は以前から発表されていたが、このEMIBが10個あるという話は2021年のHotChipsで公開された。これを受けて、てっきりUPIで相互接続すると「誤解して」この記事の図3と図4の推定図をご紹介した訳だが、実際はもっとすさまじかった。

今回公開されたスライド(Photo07)は、ワザとなのかDetailがぼやけていて拡大しても判らないので、ちょっと図にしてみた。図1はPhoto07のXCCの左上の拡大図である。

ちょっと古い話だが、初代Xeonスケーラブル・プロセッサことSkylake-SPの内部構造がこちらである。6×6の36個のBlockを、縦方向に3本、横方向に6本のRing Busで貫く様にMesh構造にする仕組みである。Sapphire Rapidsもこれは同じであり、XCCの1つのTileは図1の様に4×5のBlockから構成される。この20個のBlockを、横方向に貫く5対のRing Busが入る(ただしSlideを見ていると、最上段のI/Fを繋ぐRing Busは他のものとはちょっと違う様で、ひょっとするとここは1対ではなく2対なのかもしれないが、図が潰れていて詳細は不明である)。

一方で縦方向は2対のRing Busが入る格好だ。ではこれを4つ繋げるとどうなるのか? というのが図2である。

要するに4つのTileの縦/横方向のRing BusをEMIB経由で直接接続する事で、内部的には8×10の80個のBlockが存在し、これを縦4対/横10対のRing Busで相互接続するという、論理的には巨大なMonolithic Die構成が出来上がったわけだ。正直舐めていたというか、まさかEMIB経由で内部のRing Busを外に引っ張り出すとは考えて居なかった。ちょっと恐れ入った次第である。

ちなみにHBMの場合、このXCCのダイから一組Core/LCCを抜き、そこにHBMのI/Fを入れる格好になる(DDR5のI/FとHBMのI/Fは別に設けられている、という話は2021年のHotChipsでIntelの関係者から説明を受けている)。Photo07ではHBMでもコアがTileあたり15個ある様に描かれているが、実際にはHBMは最大構成のXeon Max 9480/9470でも56core(つまりTileあたり14core)であり、これはXCC用の図をそのまま転用しただけと考えられる。