AMDは9月29日、2025年までにAI/HPCの性能効率を2020年比で30倍に改善する、とした新たな取り組みを発表した。この詳細(?)について、Sam Naffziger氏(SVP, Corporate Fellow and Product Technology Architect)がオンラインで説明を行ったので、この内容をご紹介したい。

もともとAMDは2014年に、25x20 Energy Efficiency Initiativeという取り組みを発表した。これは2020年までの6年の間に、電力効率を25倍以上にする、というものだ。これは最終的に31.7倍(ちなみにAMD FX-7600P vs Ryzen 7 4800Hで、3DMark 11のP-Score、それとCinebench R15のMulti-Threadテストの結果とその際の消費電力から算出)に向上という形でInitiativeを達成している。ちなみにこの25x20 Energy Efficiency Initiativeに関して、Naffziger氏が"3-in-3"という形で性能効率に関する疑問に答える動画も公開されている。

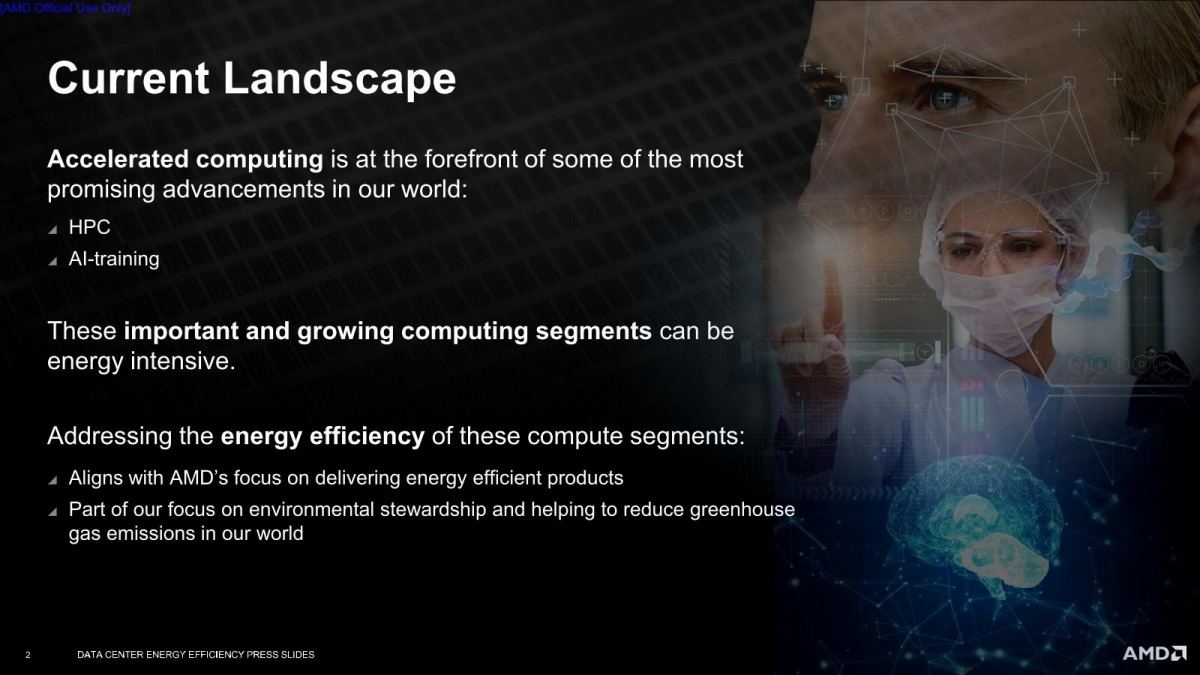

このInitiativeはコンシューマ向けの話であるが、現在はむしろHPC、あるいはAIのトレーニング向けでの省電力化が強く求められている、というのがAMDの主張である(Photo01)。実はHPCに関しては、以前からこれは強く言われつつも、未だに色々足りていない。例えばIntelが2度の問題(初代はキャンセル、2代目は納入遅延)を起したANL(米アルゴンヌ国立研究所)に納入予定のAuroraなどいい例である。もともとDoE(米エネルギー省)は、2022年に1 Exaflopsのマシンを20MWの消費電力で構築するというExascale Initiativeを掲げていた。ところがその後20MWの目標は厳しいということで、これが20~30MWとやや計画が後退している。AuroraはこのExascale Initiative一番乗りを目指したマシンだった筈が、Sapphire Rapids/Ponte Vecchioの製造の遅れもあって、稼働はおおよそ1年遅れ程度になると目されている(公式にはどの程度遅延するかの発表はなされていない)。結果、Auroraにやや遅れて2022年中に稼働予定とされた1.5 Exaflopsの性能を持つAMDのFrontierが、Auroraに先駆けて立ち上がる見込みが出てきた。

もっと問題なのはこれらの消費電力だ。IntelのAuroraはこれも公式には未発表だが、消費電力はおおよそ60MW以下とされており、これはDoEの目標の2倍にあたる。AMDのFrontierは、このスライドでは30MWとされており、これは当初のDoEの目標だった20MW/1EFlopsを実現するものであるが、そもそもこのスライド(ISC 2021におけるインディアナ大学のThomas Sterling教授のもの)の数字がどこまで正しいかは疑問だったりする。まぁそれに、仮に2020年に1 Exaflopsが20MWで実現したとしても、その先に性能を上げるのにスケールして消費電力が増えたら意味が無いわけで、この後は更に電力効率を引き上げる必要がある。

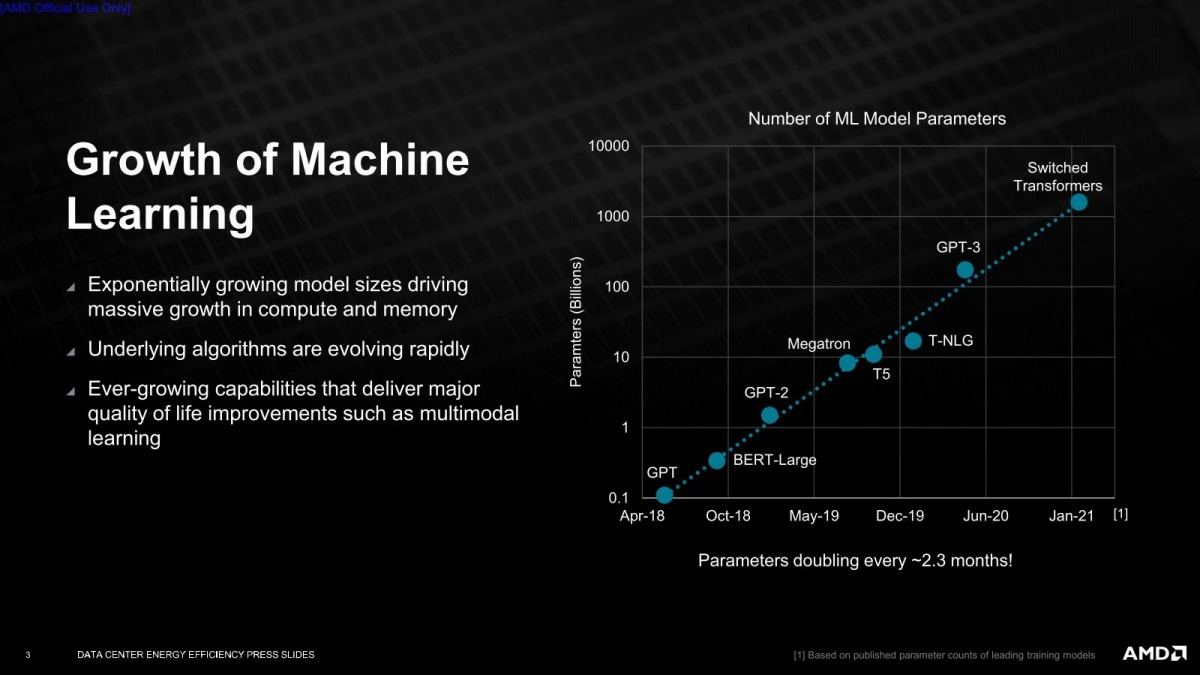

もっと凄まじいのがAIのTraninigの世界である(Photo02)。2020年のGPT-3もパラメータが1千億個とか信じられない規模であったが、今年発表されたSwitched Transformersは1兆個のオーダーに達している。ただ御覧の通り縦軸が対数軸のままほぼ直線的にパラメータが増えるというのは、グラフの下にあるように「2~3カ月でパラメータの数が倍になる」という恐ろしい世界であって、こうした新しいモデルやネットワークに対応すべく、プロセッサの性能は更に高める必要がある。

-

Photo02: もっともそのGPT-3のTrainingが1日で終わるプロセッサとかが発表されているあたり、この辺りはイタチゴッコではある。

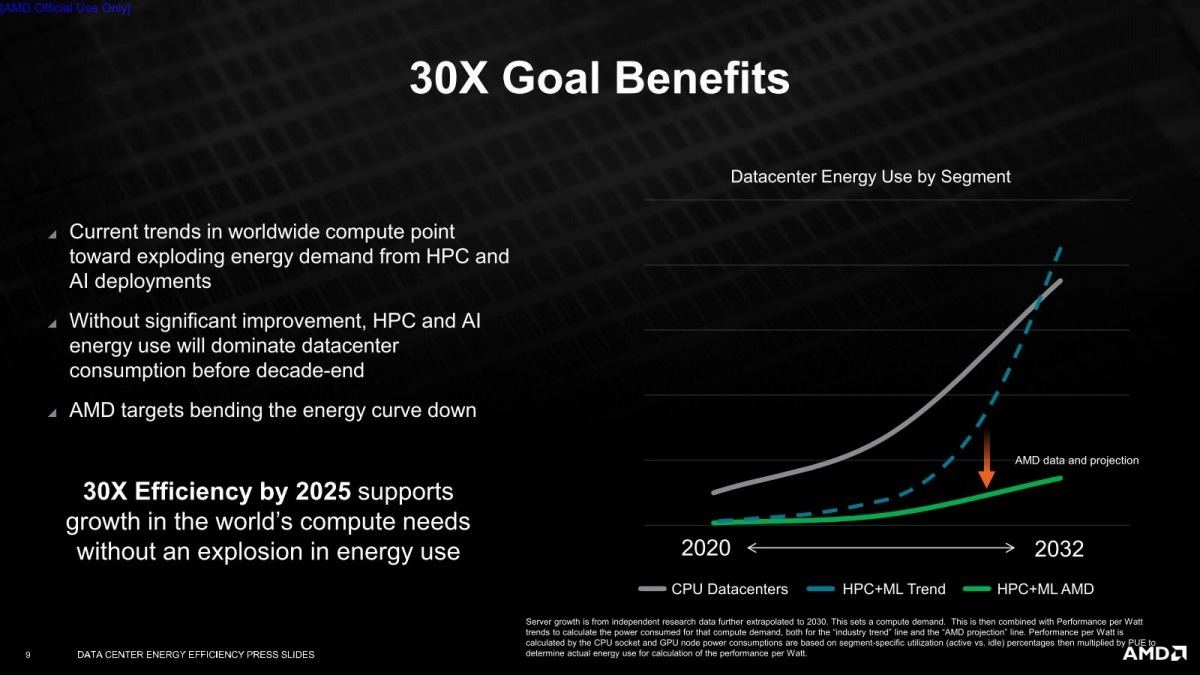

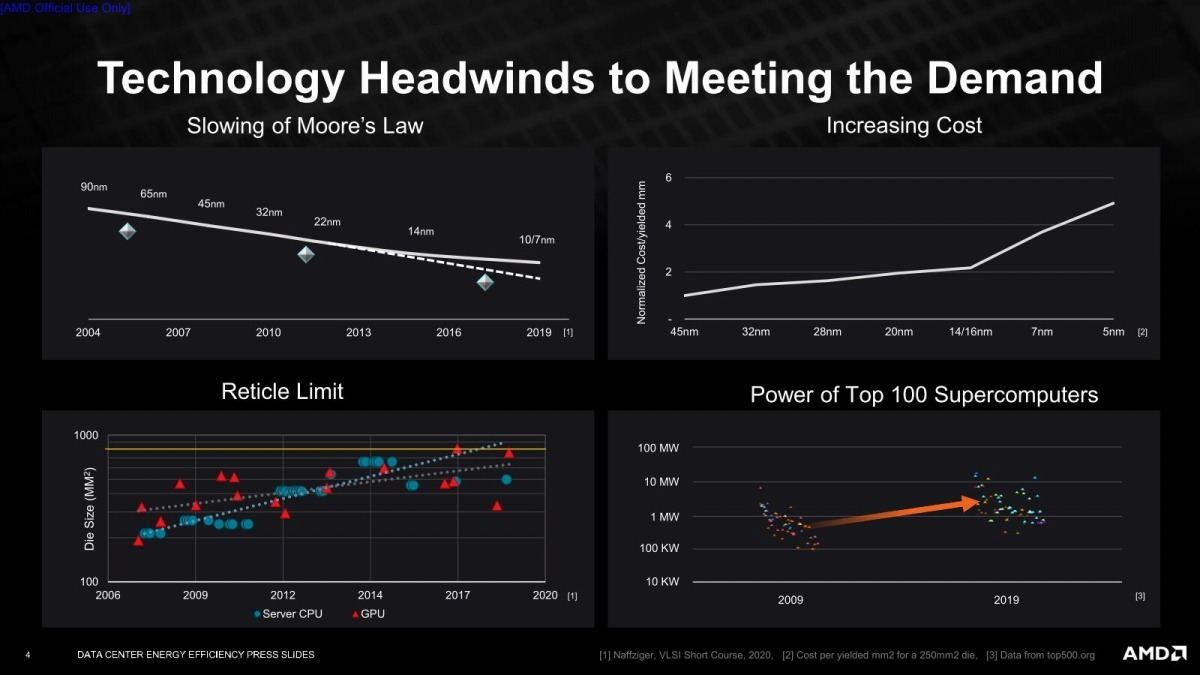

こうしたニーズに対する逆風、というのがこちら(Photo03)。プロセス微細化の遅延、ダイサイズの限界、微細化に伴うコストの増大、それと消費電力の増大の全てが、性能を高める事への抵抗要因となる。これらの全てが問題ではあるのだが、特に問題なのが消費電力であり、この調子で消費電力が増えてゆくとやがては地球全体のエネルギー生産能力に近いところまで行ってしまう、としている(Photo04)。

-

Photo03: Reticle Limitは要するに露光の際のエリアサイズの限界である。世代(というか露光機の種類)によっても違うが、600~700平方mmあたりが1回のShotで露光できる面積の限界となる。

-

Photo04: 1 ZIPS=1000 EIPSだから、1000ZIPSというのはAuroraが100万システム相当になる。まだ遠い先とみるか、間もなくとみるかは微妙なところだが、2040~2050年代にはこういう領域に達する訳だ。

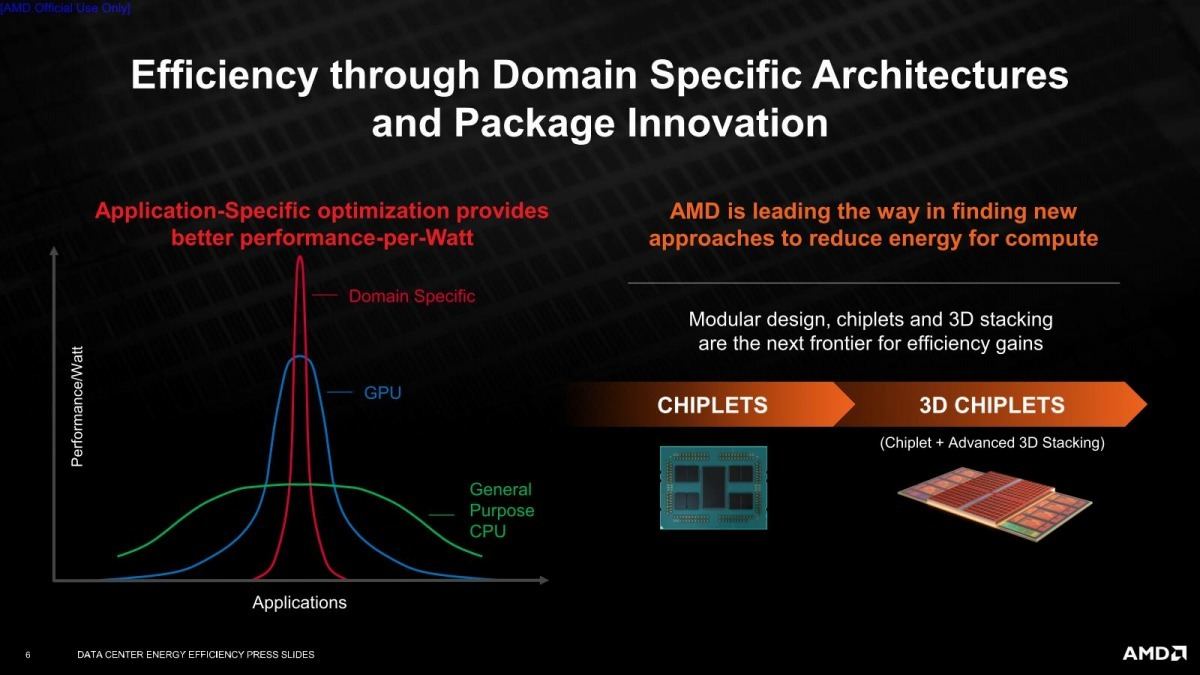

これに対するアーキテクチャ側の工夫は? というと、汎用CPUの代わりに特定アプリケーションに向けた専用アクセラレータを利用すれば、より性能効率を引き上げられるというのは前から言われていた話で、これを組み合わせるために2D/3D Stackingが有効という話もこれまた何度も出てきた話である。

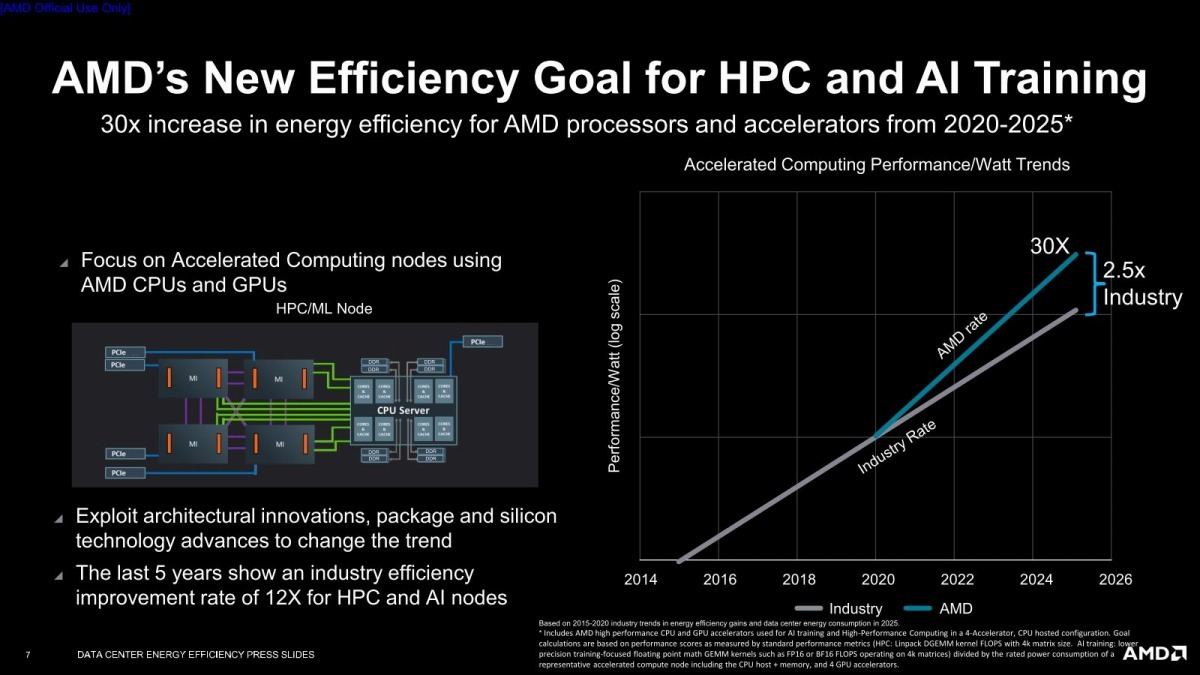

さて、直近のソリューションとして、まずAMDはHPC/AI向けにCPUとGPUの組み合わせたノードを入れるとする(Photo06)。こうしたヘテロジニアスの構成で、2025年までに2020年比で30倍の性能効率を実現する、というのが今回の発表だ。

-

Photo06: これ、どうみてもFrontierのシステム向けの構図である。ちなみにFrontierの場合、SlingShotのI/Fが各GPU(Radeon Instinct)に付くという話になっており、この構成図(紫はInfinityFabricであるが、緑はPCIeというかCCIX(or CXL)だろうか?)は中々興味ある。Ponte Vecchioは8本のXe-Linkを出すという話だが、Frontier向けのRadeon InstinctはInfinityFabricが少なくとも4本は出ていることになる(更にPCIeが2本?)。

もっともFrontierは2022年の導入だし、これに続くEl Captainも2023年だから、30倍の性能効率の実現は、これらに続く次世代(Zen 5以降)で成し遂げられることになる。具体的にそれがどんな方法で行われるか、については勿論Naffziger氏は一切語ってくれなかったのだが、Photo05の様な話がわざわざ挟み込まれる辺りは、将来のEPYCやRadeon Instinctは、IntelのSapphire RapidsやPonte Vecchioの様に複数のアクセラレータやコンポーネントを2D/3D実装を組み合わせる形で構成され、トータルで性能効率向上を目指す、という方向性を取る様に筆者には思える(Photo07)。なかなか敷居の高い数値であるが、さてあと3年でAMDは無事30倍の効率を実現できるだろうか?