日本時間の6月1日の午前11時、AMDはLisa Su CEOによるCOMPUTEXの基調講演のライブ配信を行った。現在もこちらで見直しが可能である。

さてこの基調講演の内容は事前に説明があり、こちらにその内容をまとめさせていただいたが、予想通りOne More Thingがあった。というか、このタイミングで、事前説明も無しにこういうネタをつっこんでくるあたりが今のAMDらしいといえばらしいのだが、新しい3D Packaging技術である「3D V-Cache」を搭載した製品を投入することを明らかにした。

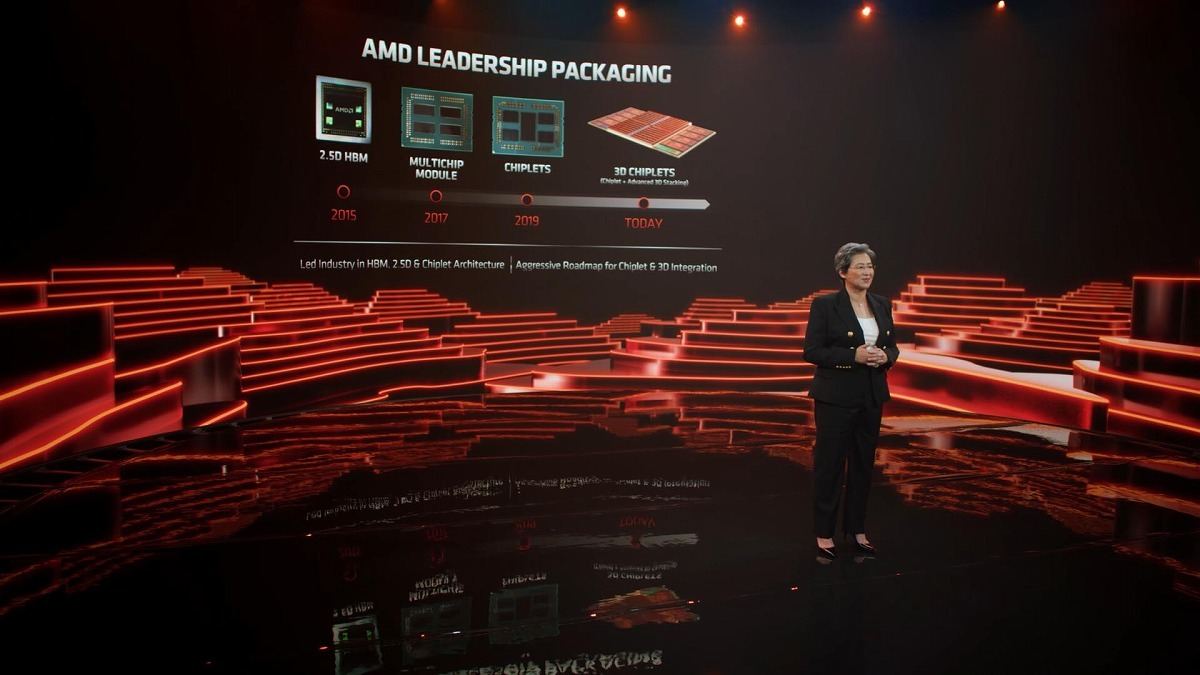

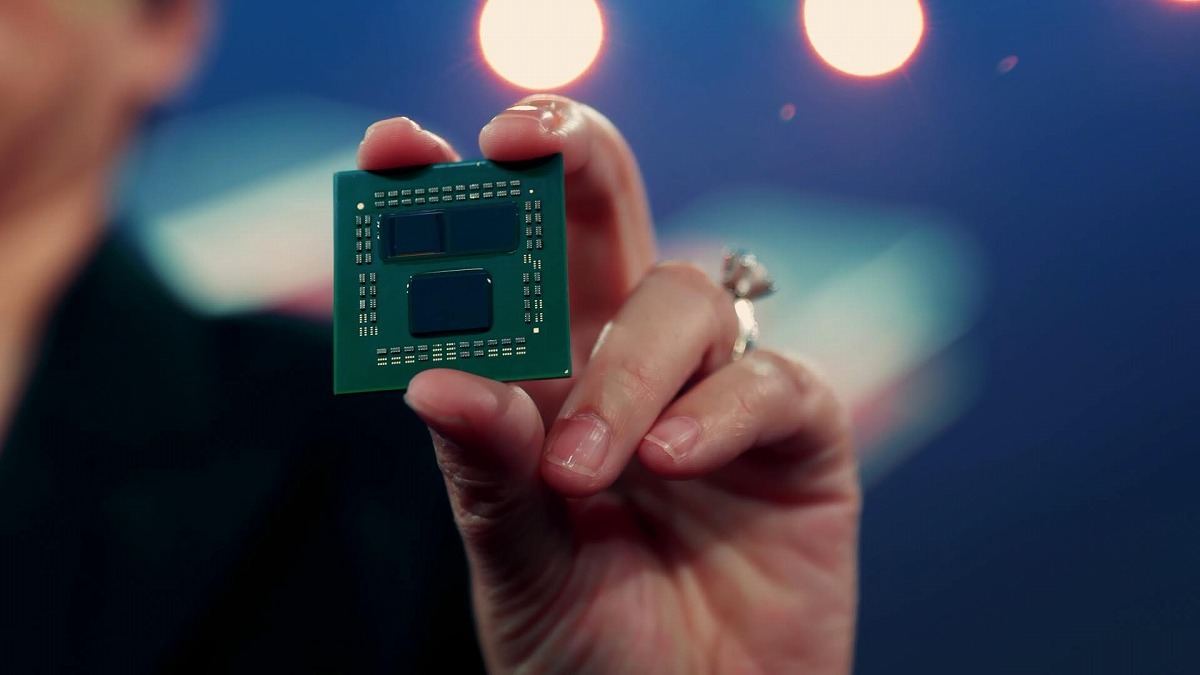

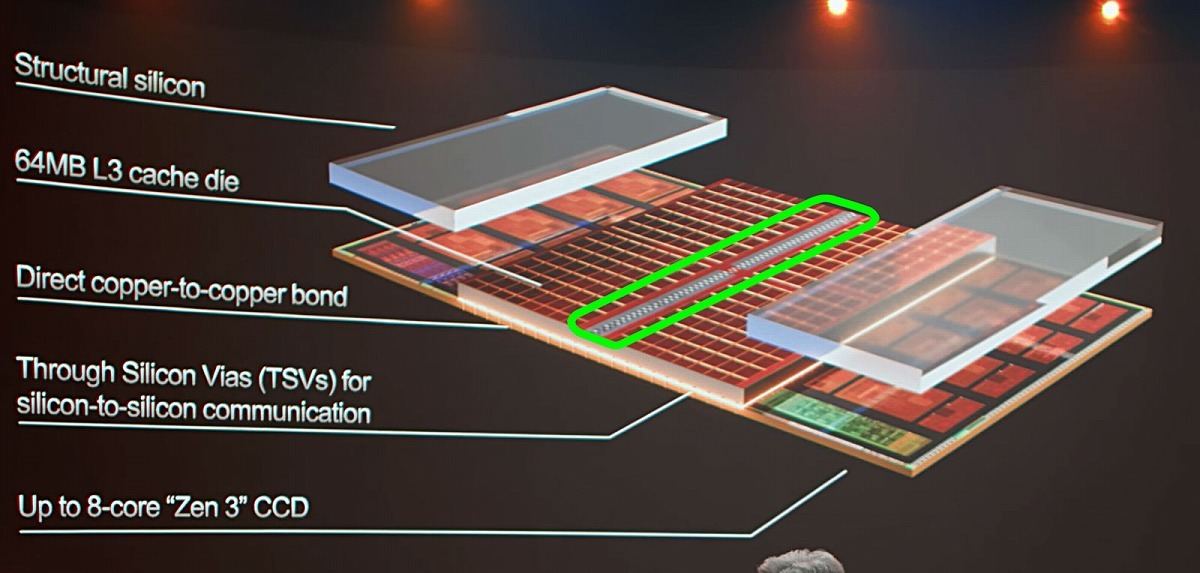

まずは基調講演の説明をご紹介したい。時間で言えば33分10秒あたり、Radeon RX 6000MシリーズとFSR(FidelityFX Super Resolution)の話が終わった後で、突如として「AMDは昔から、常に最新テクノロジーを積極的に導入してきた」と話題を転換。Process TechnologyとPackaging Technologyの両方で常に率先して新しいものを導入してきたとした上で、Packaging Technologyに関して新しく"3D Chipletを導入する"とした(Photo01)。AMDは過去数年、TSMCと3D Fabricに関して緊密な関係を築いてきたとした上で、最初の製品が3D V-Cacheになるとした。これは、既存のCPU Dieの上に追加のL3 CacheのDieを載せ、TSVで繋ぐというものだ(Photo02)。ここに搭載されるL3 Cacheは、TSMCの7nmプロセスで製造されたSRAMで、容量は64MBになるという。TSVを利用することで、この追加のL3 Cacheの帯域は2TB/secに達するとされる。

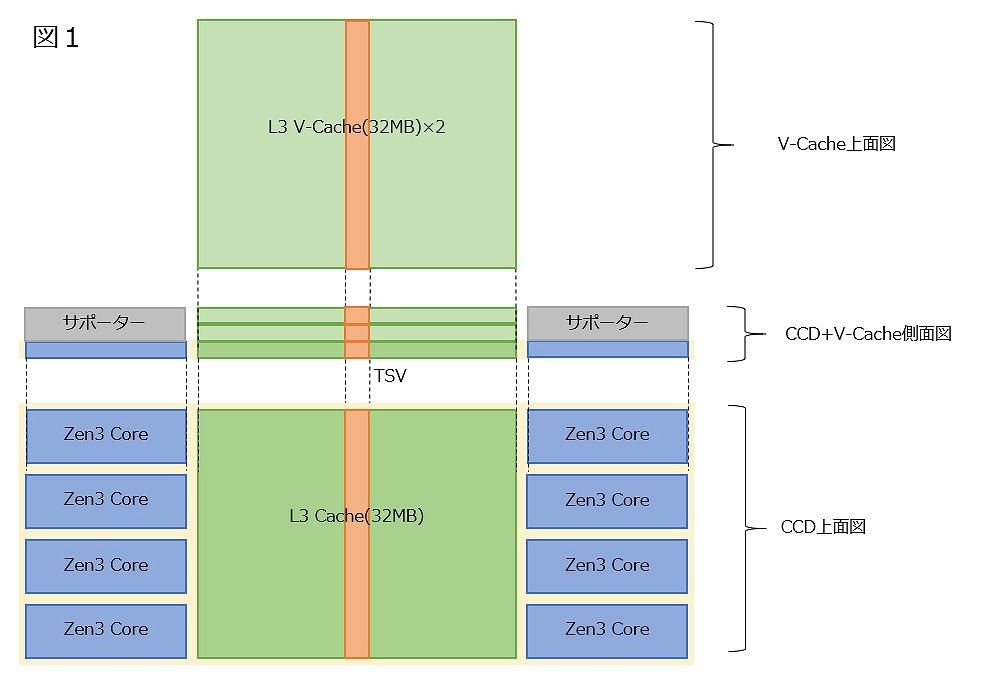

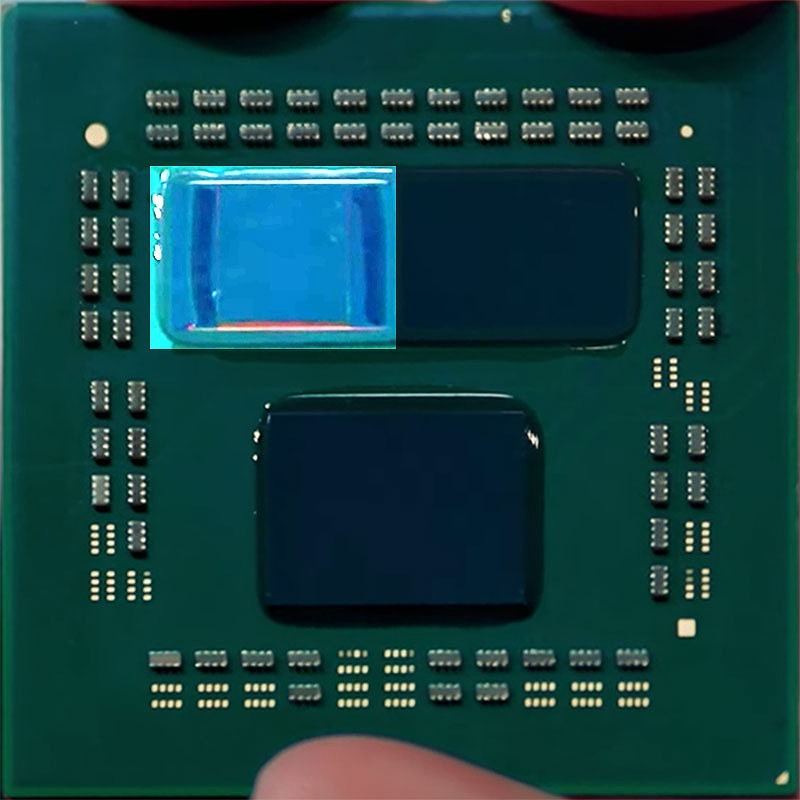

ただこのままだと追加のL3が載ってる部分と、載っていない部分の高さが異なってしまう。そこで載っていない所にはシリコンのサポーターを挟んで高さをそろえる様にしている(でないとヒートスプレッダに熱を逃がせなくなる)(Photo03)。

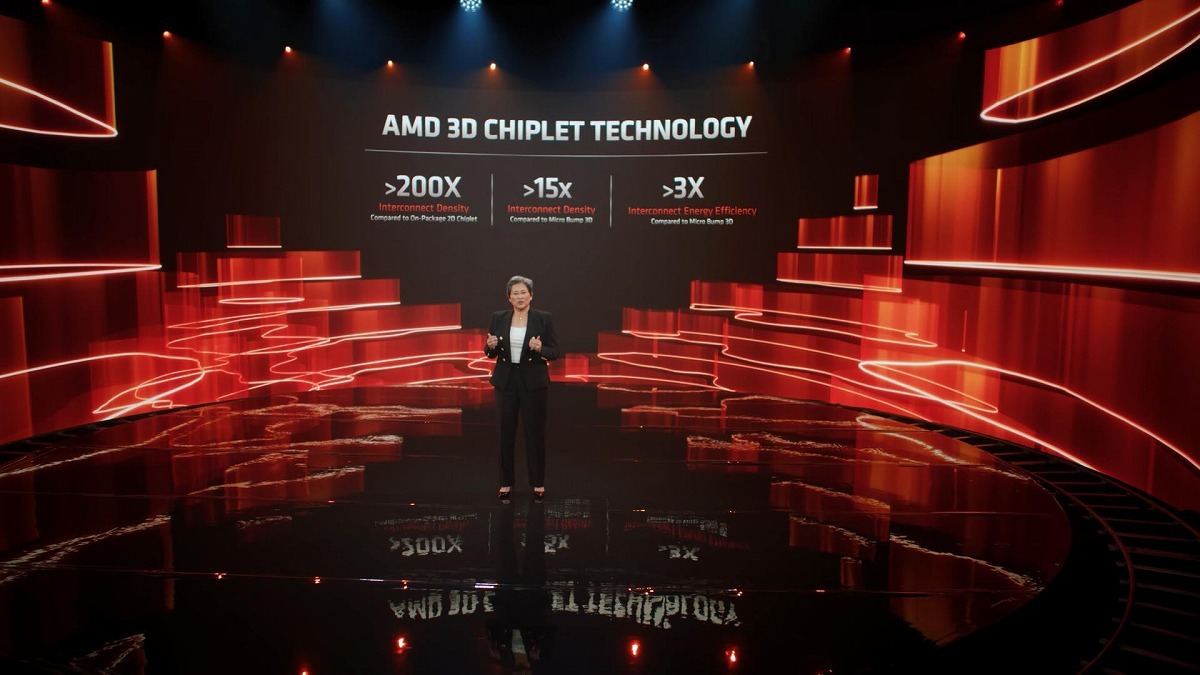

既にこの技術を採用して、L3を96MBに増量したRyzen 9 5900Xのプロトタイプが存在している(Photo04)。AMDによれば、この3D Chipletでは従来の2D MCMの200倍、Silicon Interposer(COWOS)を利用した場合の15倍の配線密度で、それでいながら転送に要するエネルギーは1/3以下になるとしている(Photo05)。

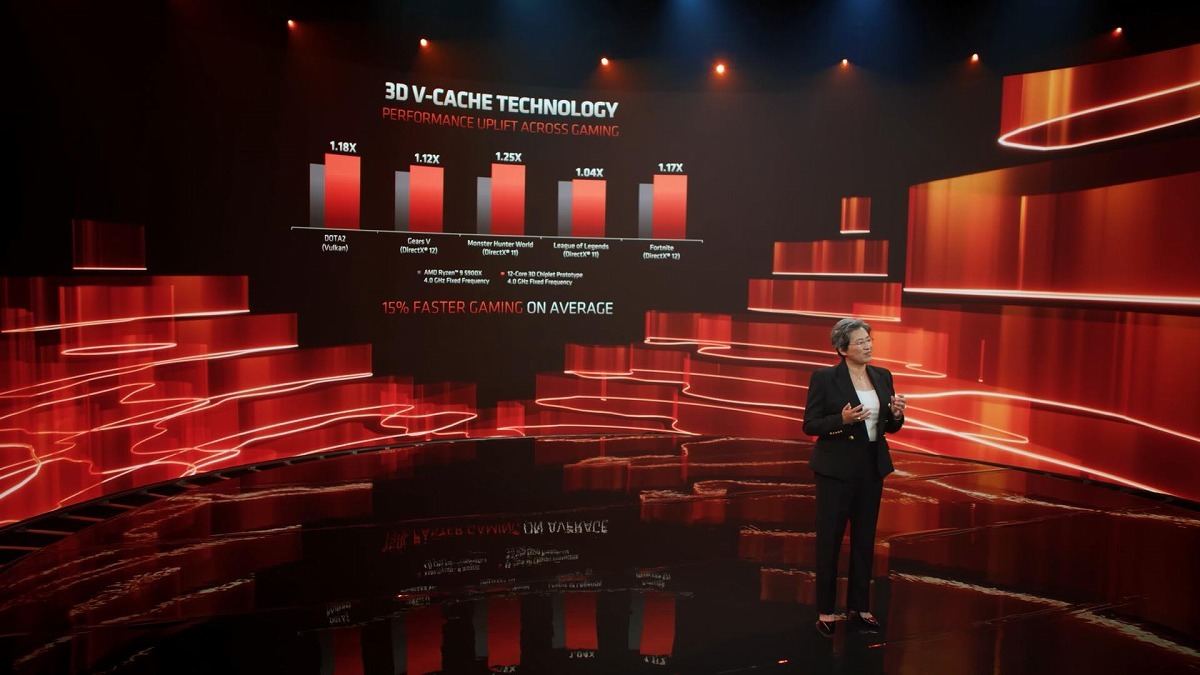

実際にプロトタイプを用いてゲームを行った場合(Photo06)、10%程度の性能向上が得られるとしている。他にも幾つか示されており(Photo07)、平均して15%ほどの性能改善が得られるとする。Su CEOは「この3D V-Cacheを搭載した製品は、年末から量産を開始する」として基調講演を締めくくった。

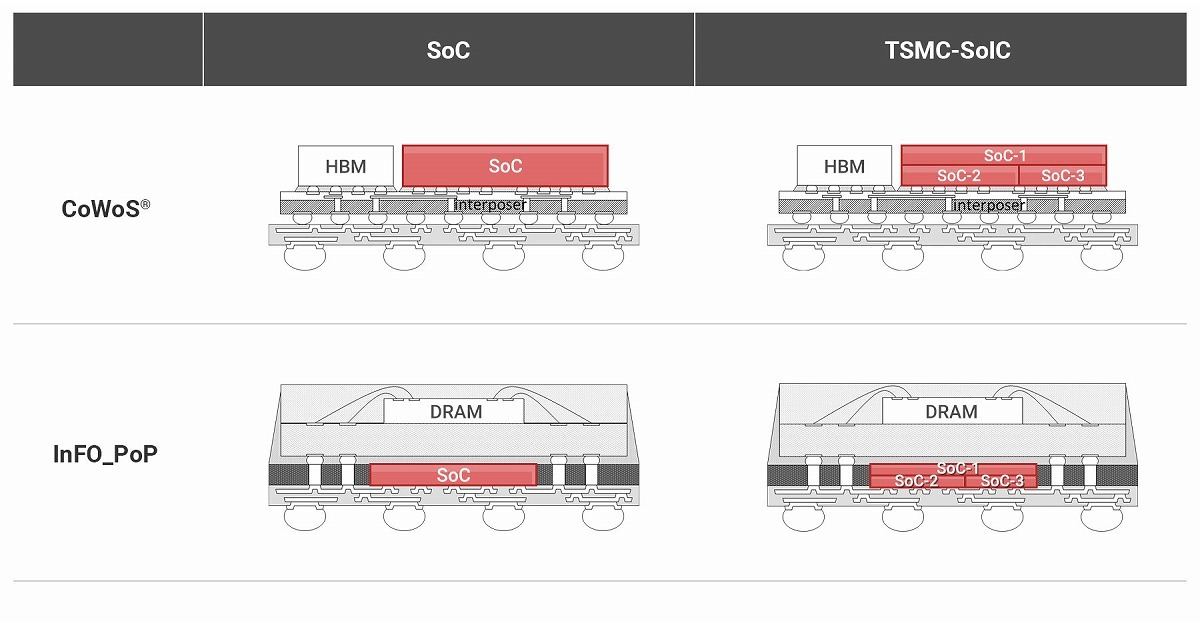

ということでまずはこれは何か? という話であるが、TSMCのSoIC(System on Integrated Chips)であることはまず間違いないと思う。SoICはTSMCの第3世代の3D Packaging技術である。第1世代はSilicon Interposerを利用したCoWoS、第2世代は特にモバイル向けに多用されているInFO(Integrated Fan-Out)、そして第3世代がこのSoICである。それぞれの違いをまとめたのがPhoto08である。

ちょっと判りにくいがTSMC的な分類で言えば

- CoWoS/Info: SoCとその他のパーツ(DRAMとかセンサーとかWirelessとか)を一つのパッケージにまとめる技術。

- SoIC: 複数のSoCを一つのSoCにパッケージする技術

という事になる。もう少し細かい話は、2019年のSymposium on VLSI TechnologyでTSMCの発表した"3D Multi-chip Integration with System on Integrated Chips (SoIC)"という論文に詳しいので、ちょっとここからご紹介する。

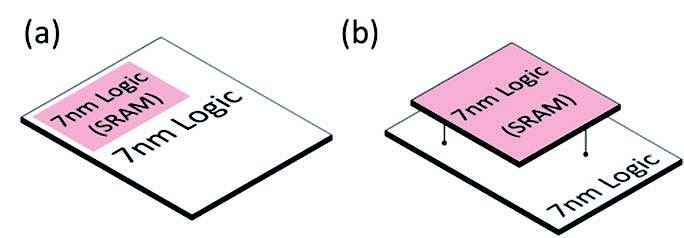

この論文では、7nm Logicチップの上に7nm SRAMを搭載する方式について論じている(Photo09)。なぜ(a)の方式では問題があるかといえば、ダイサイズが大きくなり、結果として歩留まりが下がる事になるからだ。SRAMは高密度構成にしても、ある程度の面積を喰うのは御存じの通り。Zen 3でも、ほぼダイの半分の面積を32MBのL3キャッシュで占有している。こうなると、例えばこれを96MBにするとダイサイズは倍になる計算だ。これはコストも上がるし歩留まりも悪くなる。ところが(b)の方式だと、Logic部とSRAM部は別のダイになるから、歩留まりが上がるし、LogicとSRAMの良品のみを組み合わせて最終製品を構成できるから、(a)の方式よりも無駄にするダイが減る事になる((a)の方式だと、SRAMとLogicのどちらに欠陥があっても全体がおじゃんである)。

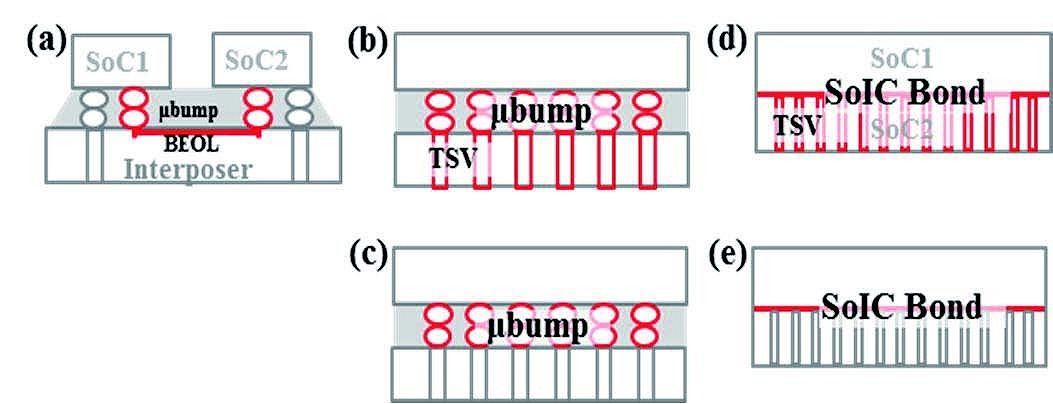

さてそのSoICの製法であるが、TSMCによればSoCの3D Stackingには5種類の方法があるという。Photo10の(a)~(e)がそれで、

(a) 2.5D Interposer: 要するにCoWoSと一緒で、μBump+1mmのBEOL(Back-End of the Line)という配線で2つのSoCを接続

(b) 3D-IC F2B: 下のチップの上面(Bottom)と上のチップの底面(Face)を、μBumpで接続。この場合、下のチップは底面にある配線をTSVで上面まで引っ張る必要がある

(c) 3D-IC F2F: 2つのチップの底面同士を、μBumpで接続する方法

(d) SoIC F2B: (b)に近いが、μBumpの代わりにSoIC-Bondと呼ばれる独自の接続方法で2つのダイをF2Bで接続

(e) SoIC F2F: (c)を、やはりSoIC-Bondで接続する構成

の5つについて比較を行っている。その結果が表1である。(c)の3D-ICを基準とすると、CoWosはBump Densityは0.8倍、速度(すべてのピンを利用しての合計の帯域)やBandwidth Density(速度×Bump Density)は0.01倍で、そのくせ転送に要する電力は23倍近いとなる。一方SoICにすると、密度は遥かに上がり、速度も上がる一方で消費電力は大幅に減る。先のPhoto05の数字で言えば、MicroBumpを使った3D接続に比べて15倍の接続密度、3倍以上の効率化というのは、この表1の(a)と(d)を比較した場合にかなり近い。

| ■表1 | |||||

| (a) 2.5D | (b) 3D-IC F2B | (c) 3D-IC F2F | (d) SoIC F2B | (e) SoIC F2F | |

|---|---|---|---|---|---|

| Bump Density | 0.8x | 1.0x | 1.0x | 16.0x | 16.0x |

| 速度 | 0.01x | 0.1x | 1.0x | 3.7x | 11.9x |

| Bandwidth Density | 0.01x | 0.1x | 1.0x | 59.7x | 191.0x |

| 消費電力(Energy/bit) | 22.9x | 3.7x | 1.0x | 0.6x | 0.05x |

問題はこの「SoIC-Bondとは何?」という話だが、ここが肝という事もあって一切説明は無い。ただ特性として、キャパシタンス(容量)がほぼ0に近いとされており、これもあって良好な伝達特性が実現するとしている。

TSMCはこのチップレベルのSoICであるSoIC-CoW(Chip on Wafer)の他に、2種類のウェハ同士を張り合わせるSoIC-WoW(Wafer on Wafer)も提案しているが、とりあえずAMDが今回"3D Chiplet Technology"として説明しているものは、SoIC-CoWと考えられる。

さて、ではAMDはこれをどういう風に構成しているかである。先ほどAMDの広報経由で確認が取れた話として、

- V-Cacheの構成は、1層で容量64MB

- V-Cacheは放熱に関しての影響は軽微である。他の3D Stackingの方式と比較しても圧倒的に優れており、従来の2Dシリコンそのままと殆ど差が無い

- V-CacheのLatencyは、L3アクセスよりもわずかに増える。一般論としてキャッシュサイズが増えればどうしてもLatencyは大きくなり、これはV-Cacheも例外ではない。ただ、64MBのL3増加に伴うDRAMアクセス頻度の低下を考えれば、V-CacheのLatency増加は問題にならない程度と考えられる

- V-Cacheの消費電力は大きな影響はない

- CCDはV-Cacheを積む関係で、薄型化されている

といったコメントをもらっている。これを勘案した上で、筆者の想定する構成は図1の様なものだ。まず下側は従来のCCDである。これは従来のZen 3ダイそのままで、薄型化の為に多少削った以外の差は一切ない。ちなみにどこを削ったか、といえばダイの裏面であろう。これは2つ理由がある。一つは本当に厚みを減らさないと、CIODよりも厚みが大きく増して、ヒートスプレッダで差を吸収しきれないからだ。

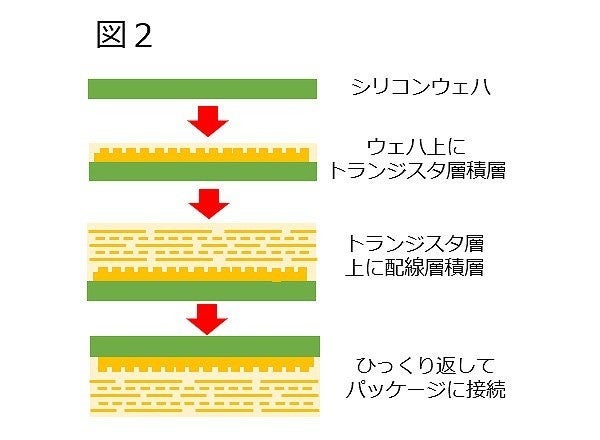

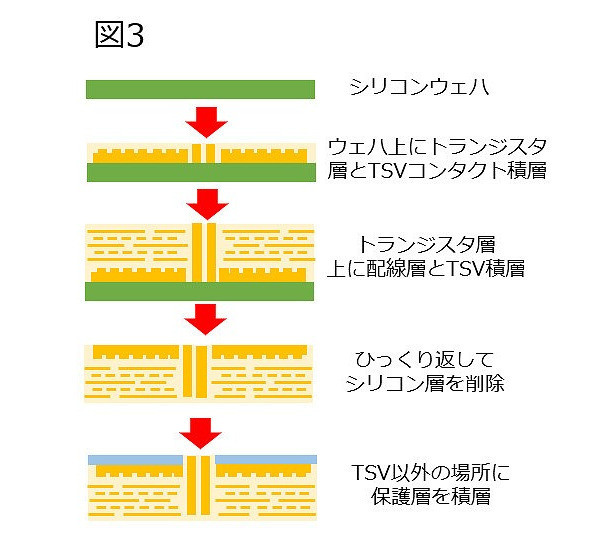

もう一つはTSVのためである。図2は従来のチップの作り方で、シリコンのうえにトランジスタ層→配線層と順に積層してゆき、完成したらひっくり返してパッケージに接続する。Flip Chip Packageというタイプのやり方である。ところがTSVを使う場合、これだと積層が出来ない。なので、図3の様に一度シリコン層を削除して、そのあとで不要な場所には保護層を改めて追加する格好になる。というか、こうしないとFlip Chipで上に別のチップを積層することが出来ない。結果、シリコン層を一度削るから厚みがグンと減る(保護層はそれほど厚みはない)ということになる。

話を戻すと、AMDの返答ではV-Cacheは1層構造で64MBとされているが、これを普通に作るのは不可能である。先にも書いたが、Zen 3では32MBでほぼダイ面積の半分を占める。だから64MBにしたら、ほぼダイサイズと同じ寸法のダイが載らないと帳尻が合わない。ところが実際にはCore Complexではなく、L3の上に重なる様に乗っている。MLC NAND Flashの様に1つのSRAMセルで2bit記憶できる方法があれば不可能ではないが、そんなものは無い訳で、物理的に32MB分の領域しかない。ここに64MBを載せるとなると、図1の様に32MB Sliceを2枚重ね、これを一つの64MB V-Cacheダイだ、と言い張るしかない。

Photo11は、Photo04を拡大したうえで、左側のCCDだけ輝度をいじって明るくしたものだ。ちょっと判りにくいが、V-Cacheのおおまかなサイズは(パッケージとの比率から)ラフに言って36~37平方mmと計算される。ダイそのものは80.7平方mmだから、概ね半分だ。いくらなんでもこれで64MBは無理だろう。ついでにTSVについて。Photo12は先のPhoto05のアップだが、ここで緑で囲んだ部分がTSVであろう、と想像される。

実のところ、このV-Cacheダイは、Zen 3のCCDからL3部分だけを抜き出したそのままだろう、と筆者は想像している。つまりZen 3の最初のバージョンから、TSVによる3D Stackingを考慮していたと思われる。勿論最初のバージョンはTSV未対応なので、内部にTSVは構築しつつ、図2の作り方で製造すればよい。そして3D Stackingを必要とする場合は、図3に切り替えればよいという訳だ。多少製造コストが上がるのはやむを得ないが、それでも96MBものL3を、既存のダイサイズ(というかダイのフットプリント)を変更せずに実現するためには非常に良い方法であろう。そしてこれは今後、製品バリエーションを増やすためにも有効な策である。Stackingなし/1層/2層/...と、L3の容量を増減した派生型製品を作りやすいからだ。おそらくRyzenよりもEPYCとか、あとはRadeon RXなどでもこの技法は有効だろう。InfinityCacheを256MB積んだRadeon RX 6000シリーズはかなり速そうだ。

昨年11月18日、NIKKEI Asiaが「TSMCのSoICの最初の顧客はGoogleとAMDで、2022年にこれを利用した製品の量産を始める」と報じたが、図らずしもこの報道が正しい事が今回の発表で分かった形になった。