IntelのProcess & Packaging Technologyについては、今年7月に開催されたIntel Acceleratedで公開されたが、このうちPackging Technologyに関しての若干の詳細が、Hot Chips 33のTutorial Sessionで説明されたので、これをご紹介したい。

Tutorial Sessionは2部構成になっており、前半の"Technology Provider: Intel packaging technologies for chiplets and 3D"は一般的というか、このところのパッケージングのトレンドと問題点、その解決策に関する一般的な話を、後半の"Case Study: Intel products built with 2.5D and 3D packaging"では、Intelの製品における応用事例を紹介する流れになっていた。まず前半であるが、HI(Heterogeneous Integration)におけるキーとして8つのFocus Areaが示され(Photo01)、Intelはこのうち赤で囲った6つの分野に対してのソリューションを提供しているという話である。

-

Photo01: 本当は8つのエリアのすべてに適切なSolutionを提供できるべき(特にFoundry Serviceを目指すなら必須だろう)なのだが、まだ手が回っていないという方が適切かもしれない。

まず一般的な配線の話に軽く触れた(Photo02)上で、当然配線密度とLine Pitchは反比例する傾向にあるわけで(Photo03)、大体Half Line Pitch(これの定義は左図にある)が5μmを切るあたりから、通常のパッケージでの実現は厳しく、Silicon Interposerあるいは別種の仕組み(EMIBなりFoverosなり)が必要、というのがIntelの主張だ。データレートと配線密度、という別の観点からの図がこちらであるが、やはり1mmあたり300pinを超えるような配線になると、もう2.5D Interposerが必要としている(Photo04)。

-

Photo02: ピン数が増える(Alder Lakeでは1700 Padだ)一方でパッケージサイズはそれほど増えないということは配線密度を上げる必要があるという意味で、これはBumpのサイズをより小さくする必要があるという意味でもある。

-

Photo04: この緑のエリアの上、つまり帯域が10Gbpsを超えるようなところで、しかもピン数が250本/mmを超えるケースは、それこそFoveros Directの様な方法しか今のところ解がなさそうだ(もっと本数が少なければ、それこそGDDR6の様に普通の配線でも行けそうだが)。

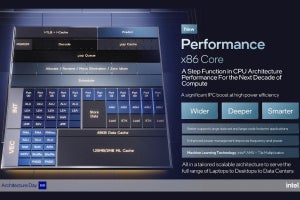

さて、Photo01に挙がった6分野のうち、上の3つ(Power-efficient, High Bandwidth On-Package IO links, Enable a diversity of off-package IO protocols, Deliver noise isolated for single ended and differential signals)に対するIntelの解がEMIBやFoveros、及びEMIB-Foverosであるとしている(Photo05)。ではほかには?というと、例えば"Support complex power delivery architectures"に対する解がオンチップFIVRである。オンチップFIVR(Fully Integrated Voltage Regulator)、つまりパッケージ上に電圧レギュレータを載せる事で効果的に電力供給を行うというのはIntelが第4世代Core(Haswell)世代で導入した方式である。パッケージ外に電圧レギュレータを置くのは、実装は楽ながら反応速度が遅いとか電源配線が難しい(ピン数が増える)という問題もあって、Haswell世代でSwitching Reguratorをパッケージに搭載した訳だ(Photo06)。

ただ次のBroadwellではFIVRではなく単なるレギュレータとなり、SkyLake世代ではオンチップのレギュレータも排された。理由は簡単で、効率が悪かったためだ。FIVRの実装にはコイルを利用したインダクタンスが必要である。FIVRはこれを配線層に実装した(Photo07)が、Load Current(つまり流れる電流)が多い場合には効果的なものの、電力が低いと効率があまり高くない。理由の一つは、スイッチング速度をかなり高くしており、電力が少ないと効率が悪くなるという話でもあるのだが、Photo07の左のグラフにあるように、2~4にしても2Aかそこそこは流れないと効率が悪いし、16 Phaseともなると10A近く流れないと90%の効率は達成できない。これに対し、実際のプロセッサに搭載されるFIVRは(Photo06にもあるが)50~300 Phaseに達する。50 Phaseとして、各々に1Aを流すとそれだけで50Wである。Desktop向けにはまだ足りないくらいだが、Mobile向けにはもうオーバーだし、UltraMobile向けには過剰に過ぎる。9W枠を50 Phaseで実装したら1個あたり180mAでしかない。こうなると効率は50%以下になる。

解決策はインダクタンスの容量をもっと高める事だが、配線層を利用する限りはそれも限度がある。そういった理由もあって使われなくなったわけだ。実はこれIntelだけではない。オンパッケージのFIVRとしてはVicorの製品が有名であり、PEZYのPEZY-SC2とかNVIDIA A100などで使われているが、いずれも100Wオーダーのプロセッサであって、10Wオーダーの用途には利用されていない。勿論コスト的な問題もあるが、インダクタンスの問題が解決できない事も関係している。そうした中で、IntelはMagnetic Inductor Arrayを第10世代から利用し始めた、というのは一つの解ではある(Photo08)。

-

Photo08: 中空コイルではなく、コイル中に磁石を入れることでインダクタンスを強めることが出来る。ただこれ、一般的なパッケージ材料ではないので、今のところFIVRには利用できず、パッケージ裏面にディスクリート部品として実装するしかないのが問題。

ちなみに別の解としてはAMDがRyzen(や最近のRadeon)で実装したLDOレギュレータの実装がある。降圧のみで昇圧は出来ないし、あまり電圧差があると損失がすごくなるので程度ものではあるが、はるかに容易に実装が出来、レスポンスも早いし、省電力プロセッサにも適している(逆に100Wオーダーのプロセッサではやや損失が気になるところだ)。このあたりはバーターになる訳だが。

"Manage increasing cooling demands"に関しては、Foveros Omni/Foveros Directが効果的と説明があったが、Foveros Omni/Foveros Direct共に配線面を向かい合わせにして接続する(Omniの方には薄いInterposerが入るが)ので、熱伝導という点では効果的であるとする(Photo09)。まぁ3Dより2Dの方が、放熱に利用できる面積が大きくなる分、放熱には当然有利ではある。

-

Photo09: というか、こちらの最後でも触れたが、どちらも2023年以降に提供の技術をサラッと「今ある技術」の様に書かれても困るのだが。

そして最後、"Provide cost effective, high precision quick turn assembly"は、同社がもともとバックエンド側にも色々な力を入れている事を説明している(Photo10)。まぁIntel Centric Viewだから、半分同社の提供するバックエンドのソリューション紹介になってしまっているのは致し方ないだろう。

-

Photo10: この辺は、IntelがFoundry Serviceを始めた2016年にも同じような説明があった。

さて、前半はこの程度で後半の話。まずEMIB(Photo11)であるが、EMIBが従来型のパッケージ(OPIO:On Package I/O)と比較して、帯域密度2倍/電力効率4倍という数字そのものは(スライドは省いたが)Intel Acceleratedでも出てきていた。ただその内訳が不明だったわけだが、今回改めて説明があった(Photo12)。配線密度は、何しろBump Pitchが半分(110μm→55μm)だから当然上がるが、その一方で第1世代EMIBは信号速度が最大でも5.4Gbpsというのはちょっと意外というか、意外と上がらなかったのだな、という印象である。もっともその分消費電力効率はずっと上がっているが、これは逆に言えばOPIO並みにに16Gbpsとかの信号が欲しい場合は、4Gbps×4の様にパラレルに展開する必要があるということで、Gearboxの追加の分も含めて考えると消費電力/配線面積のどちらで考えても、ちょっと微妙な感じである。既にIntelは次世代EMIBでBump Pitchを更に詰める事を公開しているが、信号速度の方は多少向上するのだろうか?

-

Photo12: MDFは「多分」Multi-Die Fabricの略。ちなみにIntelでMDFというと、かつてはMarket Development Fundという、PCメーカーに対して提供される広告宣伝用の資金の事であった。

次がFoveros。ついにFoverosの断面写真が公開された(Photo13)事で、Foverosの構造がある程度見えてきた。ちょっと意外だったのは、筆者は初代FoverosはTSMCで言うところのInFOに近い構成だと思ったのが、実際にはかなりSoICに近い構造だったことだ。Photo13の構図を判りやすく描くと図1の様になると思われる。つまり

- Base Dieは上下逆になり、Compute Dieと50μmのBumpで直接接続される。

- Compute Die/Base Dieの配線のうち、外部に引き出す信号線についてはCompute Dieの側にTSV(シリコン貫通VIA)を設け、これ経由でパッケージに接続する。

- DRAMはパッケージから外側のVIA経由で接続される。

という構造だ。ちなみに来年投入予定のMeteor Lakeは、このBumpが36μmピッチになるとしている。

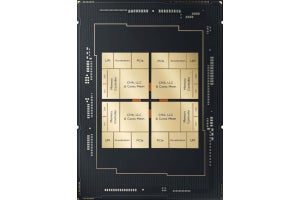

この構造が、Ponte Vecchioでも利用される。Ponte Vecchioは第2世代Foverosを利用すると見られていたが、実際D2D Pitchが36μmと記されている事でこれが裏付けされた格好だ。で、それは良いのだが先ほどのPhoto05が出た時だ。もう少し大きな図はPhoto09にあるが、この左のチップは「これは何だ?」という話である。一見するとPonte Vecchioっぽいのだが、実際には一つのチップに4 Slice分のダイが載っている。つまり本来、先日Architecture DayにおいてPonte Vecchioとして説明されたものが2つ分になる形だ。これについて、速攻でRaja Koduri氏にTwitterで問いただした猛者がおり、返事がこちら。要するに「これはこういう構成も出来るという話で実際の製品ではないよ」という返事なのだが、改めてPhoto14を見ると、表には"PCV 2T"(Ponte Vecchio 2 Tile)と記されているのが判る。

実はKoduri氏、2020年6月にこんな写真を投稿している。ここで左にあるのが、いわゆるPonte Vecchioに相当するものだが、右の2つのパッケージはその半分の1 Sliceのものと、2倍の4 Sliceのものに見えなくもない。つまり製品化するかどうかはともかくとして、Ponte Vecchio 1T/2T/4Tというものが一応世の中には存在している「らしい」事がこれらから推察できる。なんというか、まだまだ隠し玉がありそうな予感である。

最後がFoveros OmniとFoveros Directだが、Foveros Directは要するにBumpを省いて直接接続できる手法だとして、Foveros OmniはFoverosと何が異なるか? というと、要するに複数のFoverosチップを積層出来るという事に見える。なかなか複雑なIntelのPackage技術が垣間見えた説明であった。