Intelは7月26日(米国西海岸時間)、IDM 2.0戦略に沿ったプロセスおよびパッケージングの新たなテクノロジーロードマップを発表。新しいトランジスタアーキテクチャ「RibbonFET(Gate-All-Around構造のIntel独自の呼び名)」や新たな裏面電力供給方法「PowerVia」の存在を明らかにしたほか、EUVを「Intel 4」(これまで7nmプロセス世代としていた)で導入し、将来的には、高NA EUV露光装置を採用し、製造技術での技術的なリーダーシップを奪還することを強調した。

プロセスノードの呼称をx-nmから「Intel x」に変更

Intelは、今回、従来のナノメートルベースのプロセスノードの命名ルールが1997年に実際のゲート長と一致しなくなってしまって以降も、最小加工寸法としての物理的な意味合いを失ってしまったにもかかわらずx-nmのような言い方をしてきたが、10nm未満のプロセスノードの呼称については、「Intel x」(例えばIntel 7)といった表現に変更することを明らかにした。

ただしIntel 3よりも微細なプロセスの場合、「Intel xxA」(例えばIntel 20A)のように呼ぶこととするという。Aはオングストロームを意味するが、物理長は意味せず、微細化がいよいよオングストロームで計測するような超微細化の領域に入ったイメージを強調したいようである。ちなみに、TSMCはN3、ベルギーimecはi3(いずれも3nm世代)といったような独自の呼称が用いられている。

EUVの本格採用はIntel 4から

Intel 7

第3世代10nmテクノロジーとなる「Intel 7」は、「10nm Enhanced SuperFin」と呼ばれていたプロセスノードの名称を変更したもの。FinFETトランジスタの最適化に基づいて、前世代のIntel 10nm SuperFinと比較してワットあたりのパフォーマンスが約10%から15%向上するとしている。

2021年のクライアント向けCPU「Alder Lake」や2022年の第1四半期に生産が予定されているデータセンター向けCPU「Sapphire Rapids」などの製品に搭載される予定である。

Intel 4

Intel 7の後継となるのが、2022年後半から製造を開始し、2023年に出荷される製品に採用される予定のEUVを全面的に採用した「Intel 4」だという。面積の改善に加えて、ワットあたりのパフォーマンスが約20%向上するとしており、クライアント向けCPU「Meteor Lake」やデータセンター向けCPU「Granite Rapids」に適用される予定だとしている。

Intel 3

2023年後半より製造を開始する計画なのが、Intel 4の後継に位置づけられている「Intel 3」となる。FinFETのさらなる最適化とEUVの性能向上を活用することで、Intel 4比でワットあたりのパフォーマンスが約18%向上し、さらにダイサイズの改善も期待されるとしている。

Intel 20A

2024年の生産が計画されているのが「Intel 20A」で、「RibbonFET」と「PowerVia」という2つの新たなテクノロジーを投入することで実現するとしている。

Intel版Gate-All-AroundといえるRibbonFETは、2011年にFinFETを投入して以来の新たなトランジスタアーキテクチャとなる。このテクノロジーは、より小さなフットプリントで複数のフィンと同じ駆動電流を実現しながら、より高速なトランジスタスイッチング速度を実現するものだという。

一方のPowerViaは、同社独自の裏面電力供給技術であり、ウェハの表面での電力供給回路を不要とすることで、信号伝送を最適化するものだという。Intelは今回、Intel20Aプロセステクノロジーを使用する最初の顧客がQualcommとなることを明らかにした。

Intel 18A

今回発表されたロードマップの最後となる「Intel 18A」はIntel 20Aの後継で、RibbonFETの改良などによるさらなるトランジスタ性能の向上を見込んでいる。2025年初頭の投入を計画しており、ASMLとの連携による高NA EUVの早期採用や、業界初となる生産ツールの導入などを計画しているとする。

2.5D/3Dパッケージング技術も進化

Intelは、製造プロセス技術のみならず、パッケージングに関してもロードマップを更新している。

EMIB

2017年から提供している2.5Dの「EMIB」だが、Sapphire Rapidsが、EMIBを採用した最初のXeonデータセンター製品となるという。また、業界初のデュアルレチクルサイズデバイスで、モノリシック設計とほぼ同じパフォーマンスを提供としている。さらに、次世代EMIBは現行の55μmのバンプピッチから45μm、そして40μmのサポートがなされる予定だともしている。

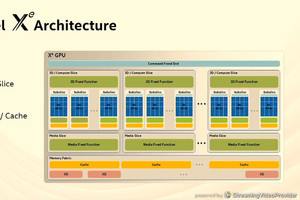

Foveros

複数種類のロジックダイを3Dに積層する技術「Foveros」。Meteor Lakeが、クライアント向けとしては第2世代技術の適用製品となり、36μmのバンプピッチ、複数のテクノロジーノードにまたがるタイル(チップレットのIntel用語)を同時に実装することで、5〜125Wの熱設計範囲で使用できるようになるとしている。

Foveros Omni

次世代Foverosテクノロジーの1つが「Foveros Omni」と呼ばれているものである。ダイツーダイの相互接続およびモジュラー設計を採用することで、複数の表面のダイ(トップダイ)タイルと、その下に置くダイ(ベースタイル)を、世代を超えて混載することを可能にするという。2023年に大量生産の準備が整う予定だとしている。

Foveros Direct

もう1つの次世代Foverosテクノロジーが「Foveros Direct」。低抵抗相互接続のためにCuとCuの直接ボンディングを、サブ10μmのバンプピッチで提供することで、ウェハプロセスの終了とパッケージング工程開始の境界、つまり前工程と後工程の境界をあいまいにし、3Dスタッキングにおける相互接続密度を桁違いに増加させることを可能にするとしている。Foveros Omniを補完する位置づけの技術で、こちらも2023年にも準備が整う予定だとしている。

なお、Gelsinger氏によると、Intel IDM 2.0戦略にとって、パッケージングはムーアの法則の利点を実現するためにさらに重要になってくるという。また、こうした先端パッケージング技術を提供するIntel Foundry Service(IFS)の最初の顧客はAmazon Web Service(AWS)となる予定だという。