フランスの国立研究機関であるCEA-Leti(電子情報技術研究所)は、Intelとプロセッサ向けの高度な3Dパッケージング技術の開発に関する協業を開始したことを発表した。

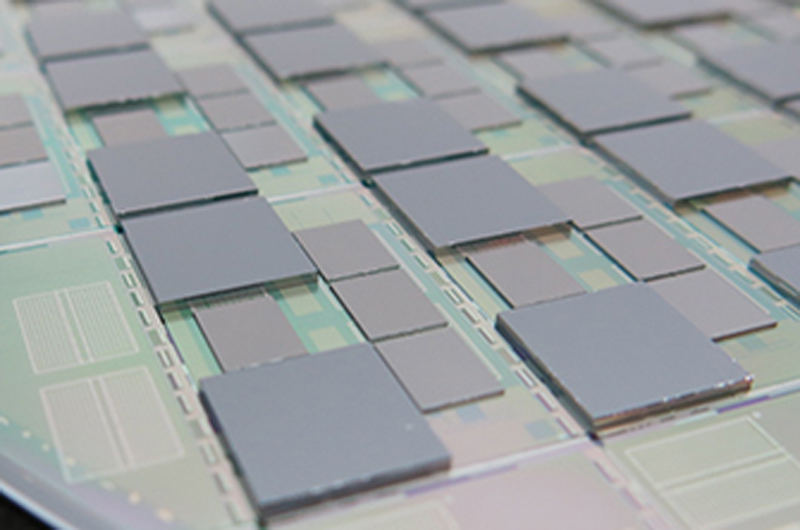

今回の協業の対象は、小型チップレットの組み立て、マイクロプロセッサのさまざまな要素間の相互接続技術の最適化、および高性能コンピューティング(HPC)ための3D ICの新しいボンディングならびにスタッキング技術であるという。Letiは、ベルギーimec同様、世界中の半導体企業から有償で研究受託するオープンイノベーションのビジネスモデルで研究を行っており、今回の契約も実質的にはIntelへの技術供与であろう。

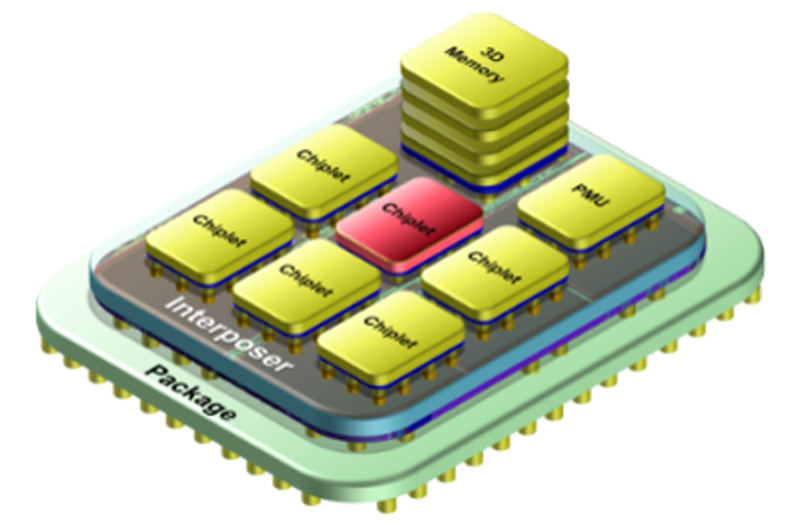

デバイス内でチップを垂直にスタック(積層)する3Dテクノロジーは、コンポーネント間の高度なパッケージ相互接続によりチップの電力を最適化するだけでなく、異種チップレットを集積することができる。これにより、最終的には、より効率的で、より薄く、より軽いマイクロプロセッサの製造が可能になる。さらに、単一のパッケージに複数の異種ソリューションを実装することにより、Intelは、異なるIPを持つことなるテクノロジーブロックを組み合わせられるようになるほか、メモリとI/Oチップを同じコンポーネント内に統合するなど、高い柔軟性を得ることができる。これにより、Intelは顧客やパートナーのニーズに対応できるようになるという。

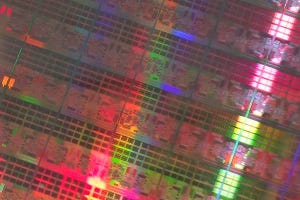

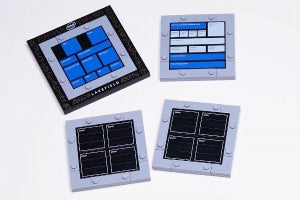

2019年、Intelは3Dスタッキング技術「Foveros」を導入している。Lakefield(開発コード名)に採用されたこの技術では、小型パッケージによる基板サイズの縮小と、性能とエネルギー効率の最適なバランスを確保できるようになったとしている。

一方、CEA-Letiは、2020年6月に開催されたIEEE Electronic Components and Technology Conferenceにおいて、3Dヘテロ集積に向けたシリコンアクティブインターポーザーに関する発表を行い最優秀論文賞を受賞している。Letiでは、両者のこれらの先端実装技術の成果を組み合わせることで、将来のHPC向けに最適な高効率デバイスを実現できるようになるとコメントしている。