2月15日~20日にバーチャル形式で開催された半導体回路の国際会議「ISSCC 2021」で、台湾TSMCのMark Liu会長(前CEO兼社長)が「Unleashing the future of Innovatuon (イノベーションの将来を解き放つ)」と題した基調講演を行った。

同氏は、国立台湾大学を卒業後、カリフォルニア大学バークレー校に留学し電気工学を専攻し博士号取得。その後、IntelやBell Labsに勤務した後、1993年にTSMCに入社し、同社の技術力を世界トップレベルに押し上げた国際的な経営者である。

3nmプロセスの量産は計画通り、2022年に開始予定

Liu氏による基調講演のなかで、もっとも注目を集めたのは「TSMCの3nmプロセスを採用する生産計画は順調に進んでいる」との発言だった。同氏によると、TSMCは過去5世代にわたり、2年に1世代の割合でロジックプロセスの微細化を進めてきており、3nmも計画通りに2022年中に量産を開始する見通しだという。ちなみにLiu氏は、「on track」という言葉を選んで使っており、一部の台湾のメディアが「3nmは計画より早く進んでいる」と同氏が述べたと伝えているが、その報道は正しくない。

なお、TSMCでは3nmプロセスまでは、従来のFin FET構造を採用することにしており、3nmからゲートオールアラウンド(GAA)構造の採用を計画しているSamsung Electronicsと見解が分かれている。両社の見解の相違は7nmプロセスへのEUVリソグラフィ導入でも生じていた。現在、両社は7nmプロセスの一部にEUVリソグラフィを採用しているが、初期の段階では、EUVに固執し、ASMLでのEUV量産技術の完成を待ったSamsungに対して、TSMCはEUV量産技術の実用化を待たずに、実証済みの液浸ArFリソグラフィの多重露光を採用して7nmの量産を先行させた経緯がある。

TSMCは、すでに台南の新工場に3nmに対応した製造装置の搬入を行っており、今年末までにリスク生産を始める計画としている。同社によれば、3nmプロセスは5nmプロセス比で、トランジスタ密度が1.7倍に増加しつつ、演算速度が11%増加する、あるいは消費電力を27%減らせるようになるという。

日本で素材開発を行うTSMCの3D ICとは?

TSMCは、2021年2月9日開催の取締役会にて3D IC向け材料の研究所を日本に自社資本だけで設置することを決定した。詳細は明らかにされておらず、今回の講演の中でもLiu氏は、この事実に一切触れなかったが、今後のシステム高集積化の切り札としての3D ICについては、時間の関係で深くは立ち入らないとしつつも言及を行った。

1960年代初頭、Fairchild SemiconductorでRobert Noyceが世界初の集積回路を商品化して以降、チップレベルでのトランジスタの集積化がムーアの法則にしたがって半世紀以上にわたって続いてきた。

この間、プロセスの微細化を進めるために、さまざまな材料や構造などが導入されてきた。こうした技術の革新により、最新のGPUでは500億個のトランジスタが搭載されるようになった。

一方、複数の半導体チップ(あるいは従来のSoCチップを機能ごとに分割したチップレット)をパッケージ基板上に接近して並べてシステムを構成するシステムレベルの集積を行うと、集積度は飛躍的に向上し、最新の製品では3000億個のトランジスタを1パッケージに収納することができるようになった。TSMCは、CoWosやInFOといった独自のシステムレベルのパッケージング技術を開発、提供してきており、今後は 「TSMC-SoIC」と呼ばれる3次元集積パッケージング技術を導入し、さらにトランジスタ搭載数を増加させることにしていると同氏はロードマップを示した。

4種類あるTSMCのシステム集積手法「3DFabric」

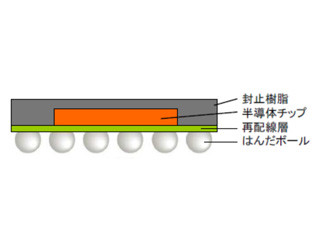

TSMCのシステム集積手法(同社は総称して「TSMC 3DFabric」と呼んでいる)だが、すでに2種類が実用化され量産導入されている。1つ目が「InFO(Integrated Fan-Out)」で、一般には、Fan-Out Wafer-Level Packaging(FOWLP)」と呼ばれる実装方式のTSMC独自の呼び方である。シリコンダイの外側にパッケージの入出力端子の領域を広げたことを特徴とする。外側の領域があることで、1000ピンを超える入出力端子を処理可能にするとともに、マルチダイの搭載を実現した。シリコンダイの入出力パッドからパッケージの入出力端子へと入出力信号を再配置する高密度な配線層は「再配線層(RDL:Re-Distribution Layer)」と呼ばれており、薄膜プロセスで形成する。

2つ目の「CoWoS(Chip-on-Wafer-on-Substrate(樹脂基板の上のウェハ、さらにその上のチップの略)」で、樹脂でできたパッケージ基板の上に、BEOLプロセスを用いてシリコンウェハ上に多層配線を形成したインターポーザと呼ばれる中間基板を配置し、その上に複数のシリコンダイを横に近接して並べるものである。後述する本格的な3D ICに対して、インターポーザを使ったCoWoSは2.5D IC(2.5次元集積回路)と呼ばれることがある。

最近では、Chip-Stacking(チップを縦方向に積み上げる方式)やWafer-Stacking(ウェハを縦方向に積み上げる方式)でシステムを構築する、より難度の高いSoIC(Systems on Integrated Chips)が開発されている。

SoICはさらにCoW(Chip on Wafer)とWoW(Wafer on Wafer)に細分化される。SoIC構造では、複数の半導体チップ(あるいはウェハ)をバンプレス相互接続でスタックできる。これにより、1つのチップからの信号を別のチップに最短距離で伝送できるようになる。

こうなってくると、もはや前工程(ウェハプロセス)と後工程(アセンブリ)の垣根は取り払われてしまって、一体化してくる。そのため、3D ICはすべてTSMCは自前の先端クリーンルームで行うというわけである。だからこそ、日本にやってくるのは伝統的な「後工程」の研究所ととらえていては判断を誤りかねない。

12個のチップ積層に成功、実用化のカギは熱放散

TSMCは、すでに12個のアクティブチップを縦に積み上げで互いを低温ボンディングで結合した3D ICの試作に成功しており、その積層厚は600μm未満に収まったという。

実用化には、熱放散の課題解決が必須であるとLiu氏は指摘する。日本に設置される予定の3D ICの材料研究所では、熱放散材料の研究が中心になるのではないかとのうわさが日本国内で出回っているが、TSMCは研究内容や研究パートナーをいまのところ一切公表していない。

今後のシステム性能向上の切り札となるSoIC

Liu氏は、講演の中でフリップチップ、InFO、CoWoSやそれ以前のI/O密度と相互配線ピッチの推移とSoICや究極のモノリシック3Dデバイスに至る新規実装技術のI/O密度と相互配線の予測を示し、「TSMCは、2011年からCoWoSを多くのデバイスに適用してシステムの集積密度を上げてきた。今後、SoICを採用することによりI/O密度は飛躍的に上がっていく。究極的には、大昔から提案されてきた理想的なモノリシック3D構造の実現が期待されるがだいぶ先になるだろう」と今後の展開を述べた。

性能に対するエネルギー効率は2年で2倍に向上

世界中の国々が脱炭素化に舵を切り、データセンターの省電力化を中心に半導体デバイスの電力効率向上がこれまで以上に求められるようになってきた。

これまで発表されてきたGPUのエネルギー効率性能(スループット×スループット/消費電力)をプロットしてみると、微細化が16nmプロセスころまでは、High-K/Metal Gate(HKMG)などの等価比例縮小と呼ばれる手法で改善が図られてきた。

High-Kを採用すると絶縁膜は厚くなるので比例縮小側に反するが酸化膜等価膜厚としては薄くなるので等価比例縮小という言葉を使っている。16nmより先の微細化は、新たなトランジスタ構造や新材料を次々導入することにより性能に対するエネルギー効率を2年で2倍に高めることに成功してきた。今後も、エコシステムを形成する素材メーカー、装置メーカー、プロセス技術者、回路設計者、システムアーキテクト、それに世界中のアカデミアが協力し合うことでエネルギー効率性能は2年に2倍の割合で改善されていくだろうとLiu氏はオープンイノベーションの重要性を訴え、そのためのプラットフォームをTSMCが準備していることを強調していた。エネルギー効率向上に3D ICは重要な役割を果たすことになるだろう。