ムーアの法則は終わらず

ベルギーの独立系半導体ハイテク研究機関imecが、毎年、東京で開催してきた同社の年次研究紹介イベント「imec Technology Forum(ITF)Japan」だが、今年は新型コロナウイルスの感染拡大を勘案し、オンライン形式にて11月18日に開催された。

冒頭、imecのCEO兼プレジデントのLuc Van den hove氏は同社の研究の全体像を紹介する基調講演の中で、同社とASMLが密接に協業して次世代高解像度EUVリソグラフィ技術である高NA EUVリソグラフィ技術を実用化することで、ムーアの法則を終焉させることなく、プロセスの微細化が1nm以下になっても継続していくことを強調した。

-

ITF Japan 2020で講演するimec CEO兼プレジデントのLuc Van den hove氏。「ムーアの法則は終焉しない」ことを強調していた (出所:ITF Japan 2020を筆者がスクリーンショットしたもの)

日本の半導体企業をはじめとして、多くの半導体企業が「ムーアの法則は終焉した」、あるいは「コスト高で無益だ」として、プロセスの微細化から次々と撤退していったが、imecは終始一貫、ムーアの法則の延命を唱えて、今や世界最先端の微細化研究機関となった。

超微細化に必須のEUV露光技術についても、日本の露光装置メーカーが開発段階で撤退する中、ASMLとともに、社運を賭けて技術開発を進め、今日に至っている。

imecが1nm超に至るロジックデバイスロードマップを公開

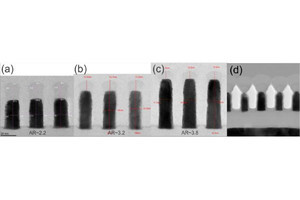

imecは、ITF Japan 2020において、3nm、2nm、1.5nm、そして1nm超に至るロジックデバイスの微細化に向けたロードマップを示した。

最上段の技術ノード名の下に記されたPPはポリシリコン配線のピッチ(nm)、MPは細密メタルの配線ピッチ(nm)である。技術ノードは、過去には、最小加工寸法やゲート長を指していたが、今では、特定の箇所の物理長を意味しない単なる「ラベル」である点に留意する必要があろう。

ここに示されたBPR、CFETや2D材料を用いたチャネルなどの構造や材料についてはすでに個別に発表されたものである。

さらなる微細化に必須となるEUVの高NA化

TSMCとSamsung Electronicsは、7nmプロセスから一部の工程でNA=0.33のEUV露光装置を導入し、5nmプロセスもさらにその頻度を増やす形で実現しているが、2nm以降の超微細プロセスでは、さらなる露光装置の高解像度化と高NA化(NA=0.55)を実現する必要があるという。

すでにASMLでは、NXE:5000シリーズとして高NA EUV露光装置の基本設計を終えているが、商品化は2022年ごろの予定だという。この次世代機は光学系が巨大化するため背丈が高く、従来のクリーンルームの天井にはつかえてしまいそうなほどだという。

ASMLはこれまでもimecと密接に協業する形でリソグラフィ技術の開発を行ってきたが、高NA EUV露光装置を用いたリソグラフィプロセス開発に関しては、imecのキャンパスに「IMEC-ASML HIGH NA EUV LAB」を新たに設置して、そこで共同開発を進め、マスクやレジストに関しても、素材サプライヤと一緒になって開発を行う計画だという。

なお、Van den hove氏は最後、「ロジックデバイスのプロセスを微細化する目的は、従来から俗にPPACと呼ばれる、パワー(消費電力)削減、パフォーマンス(電気的性能)向上、エリア(面積)縮小、コスト(経費)削減である。微細化を3nm、2nm、1.5nm、さらには1nmを超えてSub-1nmへと進めるに際して、これら4項目に加えてエンバイロンメント(環境)に十分配慮して持続可能な社会に適合する微細プロセスの実現を心掛けていきたい」と語り、今後もプロセスの微細化を継続していく意欲を示した。