技術革新が生み出すさらなるメニーコアの時代

また、Intelはメモリ階層の充実にも熱心で、次世代のアーキテクチャではキャッシュからメインメモリに至るメモリ階層で容量10倍、バンド幅10倍、レーテンシの1/10への低減、消費電力の1/10化を目標としている。

-

IntelはCPUに直結されるキャッシュ、CPUのパッケージ内に付けられるメモリ、いわゆるメインメモリの階層で、容量10倍、バンド幅10倍、レーテンシの1/10倍、電力1/10化を目標に開発を行っている

より具体的にいうと10~数100GBの容量でレーテンシは10ns以下、消費エネルギーは0.5pJ/bitという感じである。

なお、この仕様は、現在のDRAMのメインメモリの容量のメモリを、SRAMの2次キャッシュなみの速度で動かし、1/1000の消費電力にしてくれという感じの要求である。しかし、トランジスタが50倍の速度で動作し、寄生容量が1/50に低減できれば、回路の動作スピードは2500倍となるので、全く実現不可能な仕様とは言えない。

そして、トランジスタ密度を50倍に改良して回路の動作速度を50倍にすれば、性能は2500倍となる。さらに、1/50への微細化を利用すればプロセサのコア数を2500倍に増やせる。

2500コアを集積したプロセサチップを1枚のボードに4個搭載すれば、ボード当たりのコア数は1万コアとなり、このボードを100枚使うシステムを作れば100万コアのシステムが作れる。

これからのハードとソフトの接点を考える

次にアーキテクチャが、その有用性に与える影響について考えてみよう。有用性は、そのアーキテクチャが提供する性能改善量(Performance)と、その性能改善を利用できる仕事の範囲(Generality)の積で決まる。

x86を活用する開発者は2000万人以上おり、それらのエンジニアがx86のミドルウェアやライブラリ、コンパイラ、OS、ドライバなどを使っている。

その中でもサービスやアプリレベルの開発者が多く、2000万人以上のエンジニアがこのカテゴリと見られる。仮想化や低レベルライブラリを使うエンジニアの数は50万人程度と見られる。

さらにOSやBIOSレベルの仕事ができるエンジニアは5万人程度に絞られる。

-

x86のソフトウェアエンジニアは2000万人いて、大部分はアプリケーションのエンジニアである。ミドルウェアや低レベルライブラリが扱えるエンジニアは50万人程度。OS以下の層が触れるエンジニアは5万人程度である

モバイルとクラウドの時代にはハードウェアとソフトウェアの接点は、ArmハードとAppleのOSやAndroid OS、あるいはx86ハードとLinuxであった。インテリジェンスの時代には、一億人以上のエンジニアが利用することになると考えられるが、ハードウェアとソフトウェアの接点はどのような形になるのか?

マシンラーニングの利用が急速に増えており、混合精度の計算負荷が急増している。

このため、x86 CPUでもFP32に比べて、16bitのFP16の低精度演算の並列に2個実行すると言うような命令の追加が行われている。

また、アセンブラでプログラムを書くのに比べてC、C++、Javaというように高級言語にプログラムを書くようになり、コードの生産性は指数関数的に向上している。

次の図は、x86のコード開発には忍者のように陰日向なく支えてくれる開発者たちが多く存在していることを指摘している。このような人たちの貢献は大きく、無視できない。ソフトウェアスタックの各レベルで忍者開発者をサポートすることが重要である。

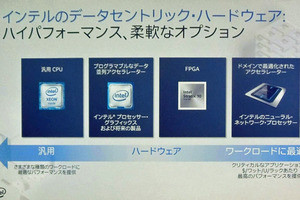

とは言え、何百万人のエンジニアを簡単に雇えるわけはなく、開発の効率を高めることは重要である。ハードウェアアーキテクチャごとに専用のソフトウェアを開発するのは効率が悪い。しかし、アーキテクチャのヘテロ性を増していくと、それに逆比例して汎用性が低下していくのも事実である。

その解決策として、IntelはoneAPIという活動を推進している。oneAPIは、ソフトウェアスタックのインタフェースを標準化する。次の図のようにアプリケーションとミドルウェアなどとのインタフェースはハードウェアとは無関係なoneAPIで標準化されるので、ソフトウェアはoneAPIに従ったインタフェース層を持つハードウェアであれば、どのハードウェアでもそのまま動作する。そして、仮想化やOS層とのインタフェースはレベルゼロのoneAPI、ファームウェアやBIOSとのインタフェースはレベルサブゼロoneAPIで抽象化されているので、それぞれのレベルでoneAPI ZeroやoneAPI Level SubZeroが一致していれば互換になる。このようなソフトウェアの作り方を推進していけば、ハードウェアごとにそれに直結したコードを作ることが必要になる部分は小さくなり、ソフトウェアの開発効率は改善する。

ソフトウェアとハードウェアの接点はスケーラブルな抽象化層で、この層がLevel Oneのハードウェア層に繋がっている。そして、ハードウェアの中にLevel Zero、Level SubZero層があり、ファームウェアやBIOS層を通してCPU、GPU、AI用のマトリクス演算器などのハードウェアを操作する。

-

ソフトウェアとハードウェアの接点はスケーラブルな抽象化層で定義され、この定義はハードウェアとは独立に作られている。ハードウェアの中もLevel Zero、Level SubZero層が定義されており、レベルが下がるとハードウェアと近くなるように区分されている

このハードウェアとソフトウェアの抽象化層の目標は、1つのトランジスタも無駄にせず、全てのトランジスタが有効に使われるようにすることであるという。