Intelは8月26日、都内で記者説明会を行い、同社が昨年からアナウンスしていたStratix 10ベースのPAC「FPGA PAC D5005」の出荷を正式に発表した(Photo01)。

Stratix 10を搭載したPACの存在そのものは昨年9月のIFTD 18の開催にあわせて明らかにされていたが、ES(エンジニアリングサンプル)としての出荷はともかくとして、正式な出荷開始には至っていなかった。元々は今年前半中に出荷したいとしていたが、これが8月まで伸びた理由は主にIntel側のFPGA PAC D5005向け開発環境の提供の準備などに予想以上に時間が掛かったから、ということだそうだ。

PACそのものは昨年のスライドのものと大きく変わらない(Photo02~05)。

-

Photo02:これはまだ評価用ということであるためか、Intelの社内利用ラベルが張り付けられているが、出荷時には無くなるはずだ。また、フランス製、というのがちょっと興味深い

-

Photo03:一見GPUカードの裏面にも見えるが、GDDRの配線はなく、その代わりFPGAを挟み込むようにDIMMスロットが上下に2本ずつ配されているのが判る

-

Photo04:100G Ethernetに対応したQSFP28が2ポート配される

-

Photo05:補助電源は8pin×1構成。ご覧の通り冷却ファンは無い(2Uシャーシ組み込みに前提だから不要という話であるが)。後端に出ているのは管理用のUSBポート(Stratix 10とは別に搭載されるMAX 10に接続されている)

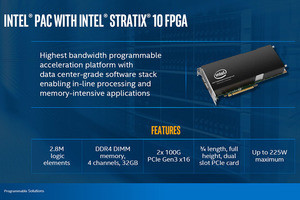

LE数は280万で、Stratix 10 SX2800を搭載する(以前の記事ではStratix 10 GX2800と書いたのだが、なぜかCortex-A53を内蔵するStratix 10 SX2800を搭載しているとの事)。消費電力は若干下がって最大215Wになったという話であった(Photo06)。また名称も他の製品にあわせて、昨年の「Intel PAC with Intel Stratix 10 FPGA から「Intel FPGA PAC D5005」へと変更したということであった。

ところでこのFPGA PAC D5005であるが、昨年の発表の際に(Intelからの単体提供ではなく)HPEからソリューションの形で提供されるという話があったが、これに関してHPEより説明があった(Photo07)。

HPEからすると、FPGAアクセラレータがサーバー市場で一番急速に伸びると予測されていることもあり(Photo08)、同社の製品の中で一番台数の出ているProLiant DL380 Gen10にFPGA PAC D5005をインストールする形で出荷を行う、という話であった(Photo09~11)。

-

Photo08:金額ベースではGPUが一番大きいが、こちらは伸びという意味ではそれほど大きくない

-

Photo09:2Uサーバー構成だが、同社によれば世界全体で見ても一番販売台数の多い製品の1つだそうだ

-

Photo10:2U(3.5inch)なので、物理的には3スロット分の拡張スロットがある形。写真では2枚が装着されているが、3枚目は左側の電源の上に装着する形になると思われる

-

Photo11:フロント側から。FPGAは背面に装着される格好に

ちなみに今のところはProLiant DL380 Gen10のみが対象であるが、これは単に検証がまだ他の製品では終わっていないからという話で、今後は対象機種を増やしていきたいとの事。さらに、9月に東京にベンチマークセンターを開設、リモートからアクセスして利用できるようにするという事であった(Photo12)。なおHPEによるFPGA PAC D5005の価格は228万円との話であった。

最後にアイベックステクノロジーより、FPGA PAC D5005に関する性能の話があった(Photo13)。

同社は動画配信サービスを行っているプロバイダ向けにトランスコード用のIPを提供するメーカーであるが、今回のFPGA PAC D5005を利用することで、Apple ProRes 4Kで4倍、XAVC Intra 4Kで5倍、HEVC Intra 4Kで30倍のエンコード性能(比較対象はAWSのM5 Instance m5.metal(vcpu=96))のトランスコード性能が実現できるとした。実際4K映像をHEVCにトランスコードするにあたり、CPU(Core i7-8700K)のみ(Photo14)とFPGAオフロードした場合(Photo15)を比較、圧倒的に高速にトランスコードが可能になった事をデモした。

-

Photo14:右上のCPU利用率では、6つのCPUがほぼ100%近い負荷でありながら、トランスコード結果はかなりカクカクしたもので、全然処理性能が追い付いていない様が示された

-

Photo15:FPGAにオフロードすると、FPGAとの通信やFile I/Oなどのために多少負荷が高いコアもあるものの、全般的に負荷は大幅に減り、それでありながらほぼエンコード速度はリアルタイムになってた

なお山崎氏によれば、今回はHPEとの協業であるが、今後は他のメーカーとも協業していきたい(以前のArria 10 PACを発表の際にはDELL EMCと富士通がパートナーとして紹介された)という話であった。