ISC 2019でのGustafson教授の発表に続いて、理研R-CCSのプロセサ研究チームのArtur Podobas研究員がFPGAでのPositの実装についての発表を行ったした。元々、Podobas氏は東工大の松岡研究室でPositを研究していた人で、松岡先生の理研R-CCS所長への転任に伴いR-CCSに移られたようである。

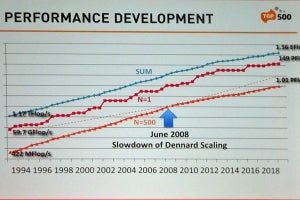

ムーアの法則の終焉が近づき、ハードウェアを増やすことが難しくなってきており、効率の高いハードウェアとして、より短いデータ表現を使ったデータ処理に関心が集まっている。データ表現の変更は色々な影響があるので、実験をして、本当に問題ないかを検証する必要がある。

しかし、シミュレーションでは実行速度が遅く、多数のケースでの実験が困難である。ASICで作れば実行速度は速くなるがお金も時間もかかるということで、FPGAでPosit演算器を作って評価したという論文である。

Podobas氏は、ハードウェア記述言語でPositの演算器を記述し、FPGAで実装した。

次の図はPositの乗算器を示す。右の図のように、デコードロジックで入力のPosit数をMantissaとRegion(指数部に相当)に分割して、乗算器に送って積を計算する。この積の計算はIEEE 754の乗算器とほぼ同じである。そして、エンコードロジックで、積をPosit数に変換して出力する。

この乗算器のハードウェア量は、Posit16の場合、ロジックブロックが206個とDSP(基本の整数の掛け算を行う)が1個、Posit32ではロジックブロックが484個で、DSPが2個必要である。パイチャートに各ロジックブロックがどの部分に使われているかの比率が載っている。

同様に、加減算部はPosit16の場合はロジックブロックが300個、Posit32の場合はロジックブロック657個を必要とした。

そして、比較器とAbs、MaxはPosit16ではロジックブロックが7~17個、Posit32の場合は14~33個となっている。

次の図は、Stratix V FPGAで作ったこれらの演算器の動作クロックを示す図である。左のグラフは掛け算器で、3本の折れ線グラフは、Positのesが2、3、4の場合である。グラフに見られるように、最大クロックは、ほとんどesの選択にはよらず、おおよそ400MHzから600MHzのクロックまで動作している。

右のグラフは加減算の場合で乗算器より多少速いクロックで動作している。

ベクトルの加算、内積、行列式とステンシル計算でPosit16とPosit32についてソフトウェアシミュレータ、Stratix V FPGA、Arria 10 FPGAを使った場合の性能を示している。単位はGFlopsで値が大きい方が性能が高い。

ベクトル加算と内積は、なぜか分からないが、このグラフではほとんど見えない程度の性能になっている。行列積とステンシル計算はシミュレータの場合の性能は棒グラフでは見えないが、2種のFPGAを使った場合の性能は見られる。それぞれのベンチマークで、左の2本のペアの棒グラフがPoist16、右の2本のペアの棒グラフがPosit32での演算である。そして、各ペアは左側がStratix V、右側がArria 10を使った場合の性能である。

行列積では、Posit16 に比較してPosit32の性能は1/4程度と大幅に低下している。一方、ステンシル計算ではPosit32ではPosit16 の半分程度の性能である。なぜ、このようになるのかは分からない。

また、当然であるが、2010年の製品であるStratix Vに比べて2014年の製品のArria 10の方が性能が高く、その比率はPosit32のステンシル計算では約2倍、Posit16 の行列積では4倍程度になっている。

結論であるが、テクノロジの進歩が鈍化して、アーキテクチャの研究には面白い時代になった。FPGAのような再構成可能なデバイスは、このような試行を行うには便利である。

この研究では、Posit16では200+ GFlops、Posit32では60+ GFlopsというかなり良い性能が得られた。より新しいUltraScaleやStratix 10 FPGAを使えば、もっと性能を上げることができると思われる。