半導体研究機関であるベルギーimecは、米サンフランシスコで開催された半導体デバイスの国際会議「IEDM 2018」にて、ムーアの法則の延命を可能とする3nmおよびその先を見据えたCMOSロジックデバイスに関する発表を行なった。

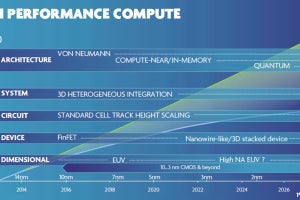

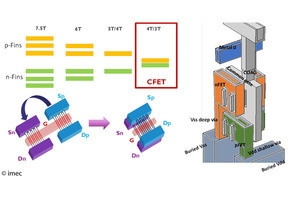

今回のIEDMにおいてimecは、 縦方向に2段積層した3nmノードのSiおよびGeゲート・オール・アラウンド(GAA)ナノワイヤ/ナノシートFETの性能向上について3件の報告を行なった。

GAA MOSFETは、従来のFinFETと比べてゲート長とゲートピッチのさらなる微細化の実現に向けた有力候補で、ナノワイヤまたはナノシートを垂直に積み重ねることによって、限られたフットプリントの下で駆動電流を最大にすることができる。前回のIEDMにおいて、imecは実際に動作する積層GAAデバイスを発表していたが、今回は、その実用化に向けた一環としてのプロセスの最適化、GAA MOSFETの歪みの効果、信頼性と劣化のメカニズムに関した報告を行なったという。

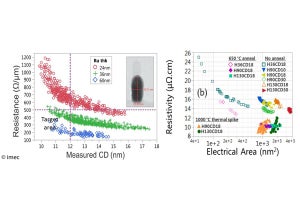

1つ目の発表は、プロセスの最適化により、ナノワイヤのサイズを低減し、電気的性能を低下させることなく形状制御性を改善させたというもの。これらの改良により、Si GAAデバイスの垂直方向の長さを削減しつつも、nMOSとpMOSのIon/Ioff性能の改善により、チャネルのマージンを短くすることに成功したとする。実験では、リングオシレータのゲート遅延を24psから10psに改善できることが確認されたとする。

2つ目の発表は、GeナノワイヤpFETとGe FinFETと比較し、主にGeナノワイヤpFETのほうがより最適な歪み効果を引き出せることを明らかにしたというもの。そして3つ目は、n-Si、p-Siおよび歪みp-GeナノワイヤFETの劣化の様子を調べることで、その劣化メカニズムの解明と安全な動作範囲を導きだしたというものとなっている。

なお、imecの特別技術スタッフメンバーである堀口直人氏は「ゲートオール・アラウンド・ナノワイヤ・トランジスタは、5nmノードを超えるあたりからFinFETを置き換える有望な候補である。今回の研究成果により、ナノワイヤGAAトンジスタを実現するプロセスの最適化が進み、かつ歪みの与え方やデバイスの劣化メカニズムなどの理解を深めることができるようになった」とコメントしている。