ホテルのチェックアウトまで15分、という急かされた状況だったこともあり、本当にあっさりとレポートしたAMDのNext Horizonイベントであるが、実際には色々と盛り沢山な内容であった。Zen 2と7nm EPYCというCPU編を、もう少し掘り下げてご紹介したいと思う。

まずは製造プロセスについて。Zen 2ではTSMCの7nm(N7)を利用する。既にAppleがA12プロセッサで用いて量産出荷を開始しているが、これを別にすれば、ほぼ業界の先頭を切っての採用となる(何しろTSMCにとってAppleは超大口顧客なだけに、他の顧客とはまったく対応が異なる)。

TSMC自身はN7について、10nm世代(N10)と比較して1.6倍のロジック密度であり、20%の性能アップもしくは40%の消費電力削減が可能と説明している。もっともそのN10についても、16nm(N16FF)と比較して2倍のロジック密度と15%の性能アップ、もしくは35%の消費電力削減が可能、という話になっている。

これをそのまま勘案すると、N16FF → N7で3.2倍のロジック密度、38%の性能アップ、もしくは61%の消費電力削減、ということになるが、こんなに飛躍するわけもない。下図に示した「ロジック密度2倍、性能25%アップ、もしくは消費電力半減」というは、Fabそのものの乗り換え(GlobalFoundries → TSMC)による差はあるにせよ、概ね16~14nmノードから7nmノードへの移行では妥当な数字ではないかと思われる。

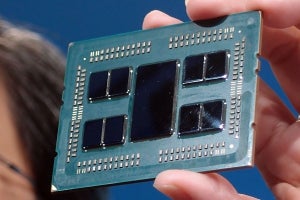

さて、このロジック密度が倍、というのは要するに、「同じ面積ならばコア数を倍に、同じコア数なら面積を半分に」ということ。実際、Lisa Su CEOが示した7nm EPYC(Photo01)のアップ(Photo02)からダイサイズを推定できる(パッケージは既存のEPYCと同じく75mm×58mmなので、ピクセル数の比から計算可能)。それによれば、

CPU:71.8平方mm

I/O:421.0平方mm

という計算になった。ただし別の写真でも同じように計算したところ、

CPU:72.5平方mm

I/O:425.3平方mm

となっていて、微妙に合ってない。まぁラフに言えば、CPUは72平方mm前後、I/Oダイは420平方mm強というあたりだと思われる。

既存のZenコアベースのダイ(Summit Ridge)が213平方mmだから、半分どころか1/3近くに追い込まれているわけだが、これはCPU側にメモリコントローラやPCIe、サウスブリッジ機能などを一切搭載しないから、その分ダイサイズを追い込める。

Photo03はSummit Ridgeの内部だが、中央の2つのCCX(Core Complex)の面積は合計で95平方mmほど。これが半減したとして47.5平方mm。これにInfinity FabricのI/O端子を追加すると70平方mm前後、というのは概ね妥当なところではないか。

ちなみに、消費電力据え置きで性能25%アップ、もしくは動作周波数据え置きで消費電力半減というのは、非常に興味深い。

まずDesktop向けに関して言えば、消費電力据え置きで動作周波数を25%引き上げられるということである。今のRyzen 7 2700Xが「Base 3.7GHz・Turbo 4.3GHz」というスペックだが、計算で言えば「Base 4.6GHz・Turbo 5.4GHz」近くまで引き上げられることになるからだ。実際ここまでは上がらないと思うが、Base 4GHzは堅いところではないか。

一方、EPYCについていえば、動作周波数を据え置きにすれば、コアの数を倍にしても消費電力が変わらない計算になる。これは特にサーバー用途では非常に大きな強みになるだろう。

またモバイル向けには現在、Raven Ridgeベースのコアが投入されているが、4コア8スレッド構成。これを8コア16スレッドにしても、消費電力が変わらないという計算になるわけで、新たな製品オプションが提供できることになる。

可能性だけで言えば、デスクトップ向けにSocket AM4のままで動作周波数を変えずにダイを倍増(つまり16コア32スレッド)させた製品を投入することも、不可能ではない。しかし、メモリ帯域とのバランスが著しく崩れるので、実現の可能性は低いだろう。