Hot Chips 26において、MITのグループは6×6のメッシュで36コアを接続し、スヌープ方式でコヒーレンスを実現する「SCORPIO」を呼ぶプロセサを発表した。

要素技術の研究だけではなくプロセサなどのシステムまで作るという研究は米国の大学にとってもハードルが高く、今回のHot Chipsの全部の発表のなかでも共著ではなく、大学単独の名前で発表されたのは、この1件だけである。

メッシュの場合、キャッシュラインのスヌープや無効化の要求などが受け取られるまでの時間は、それぞれのコアにとって、要求元のコアからの距離に影響される。このため、あるプロセサにはAの要求が先で、その後、Bの要求が到着するが、別のプロセサでは、到着の順序が逆転し、Bの事象の方が先に起こったように見えることが起こる。しかし、このように、システム全体で、事象の発生順序が統一されていないとキャッシュコヒーレンシの維持はうまく行かない。

このため、チップ内では、プロセサ間の接続にはバスやクロスバを用いて、集中的に要求を処理するという方法で事象の順番を決めているのであるが、このやり方はスケーラビリティが悪く、多数のコアを持つチップには適していない。

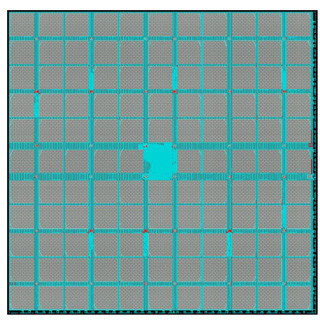

SCORPIOは、Snoopy COherent Research Processor with Interconnect Orderingのアクロニムで、インタコネクトで順序性を作ることで、スヌープ方式のコヒーレンシ処理を可能にするという方式を考案した。そして、次の図に概要を示すように、IBMの45nm SOIプロセスを使い36コアのメッシュ接続のマルチプロセサチップを開発している。チップサイズは11mm×13.5mmである。

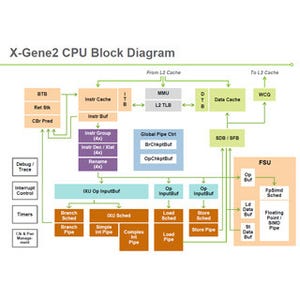

使用したコアはPowerアーキテクチャのFreescaleのe200で、もともとマルチコアでのキャッシュコヒーレンシを維持する機能をもっていないので、L1キャッシュはWrite-throughとし、L2キャッシュの無効化が要求されると対応するL1キャッシュも無効化するという設計をとっている。各コアのキャッシュの容量はL1キャッシュがI/Dともに16KB、L2キャッシュが128KBである。

そして、36個のコアを6×6の2次元メッシュネットワークで接続している。1つのネットワークノードが1つのタイルに対応し、メッシュリンクのデータパスは137bit幅となっている。

しかし、メッシュでは事象の到達順序が保証できないという問題があるので、次の図のようにメッセージ通信用のメインのネットワークに加えて通知用のネットワーク(Notification Network)を追加する。そして、通知用ネットワークは、すべてのノードで事象の発生順序を同一にする働きを持たせる。

つまり、メッセージの伝達と順序性を実現するネットワークを分離するという方式で、これは新しい考えである。

通知する事象があるノードは、自分のノード番号に対応するビットを"1"にしたフリットを作り、隣接したすべてのノードに送り出す。フリットを受け取ったノードは、また、隣接ノードへ転送し、ネットワーク全体に通知をブロードキャストする。2つ以上のポートから同時にフリットが来ると普通は衝突であるが、通知用ネットワークのルータはそれらのビットベクタのORを取って、伝達させていく。つまり、ノード1からのフリットとノード11からのフリットがぶつかると、ビット1とビット11が立ったビットベクタが作られて次へ伝達されて行く。