Applied Microは、世界で一番早くARMv8アーキテクチャの「X-Gene」プロセサを完成させた会社である。そして、今回のHot Chips 26では、第2世代となる「X-Gene 2」プロセサを発表した。

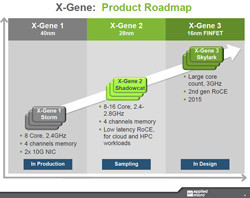

Applied Microは2013年6月にX-Gene1チップをデモしており、すでに、X-Gene1を使ったサーバがSoftIronなどから商品化されている。X-Gene1は開発時期が早かったことから40nmプロセスで作られているが、今回発表のX-Gene2では、当然、28nmプロセスが使われている。しかし、X-Gene2は単なるプロセスシュリンクではなく、プロセサのマイクロアーキテクチャを強化して性能を高め、Ethernetを使うリモートDMA機能(RoCE)をサポートするなどのデータセンター機能を強化したプロセサとなっている。

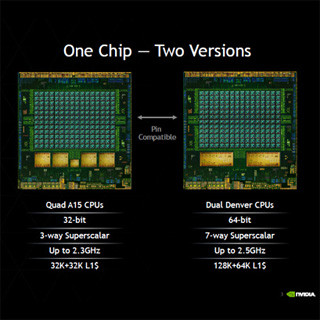

X-Gene2は8~16コアを集積し、2.4~2.8GHzクロックで動作するが、現在、開発中のX-Gene3では、さらにコア数を増やし、クロックも3GHzに引き上げる計画である。そして、X-Gene3は2015年に登場というロードマップとなっている。

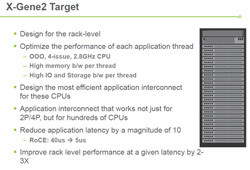

X-Gene2のターゲットはデータセンターのラックレベルのサーバプロセサである。そのため、4命令発行のOut-of-Order実行という他社のARMサーバチップと比べると高性能なマイクロアーキテクチャを採用し、スレッドあたりのメモリバンド幅、I/Oやストレージアクセスのバンド幅を高めるアプローチをとっている。

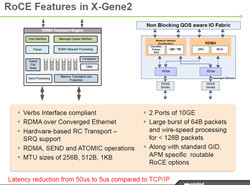

そして、何百台ものサーバが使われる環境でのアプリケーション性能を高めるために、RoCE(RDMA on Converged Ethernet)をサポートしている。通常のEthernetのプロトコルでデータを伝送すると少なくとも40μs程度の遅延が出るが、RoCEを使えば、これを5μs程度に短縮でき、ラックレベルのアプリ性能を2~3倍に高めることができるという。

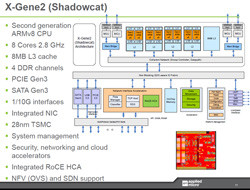

「Shadowcat」のコード名で開発されてきたX-Gene2チップは、2コアのペアにL2キャッシュを付けたモジュールを4個搭載し、それに8MBのL3キャッシュと4チャネルのDDR3/4インタフェースがついているという構成となっている。

特徴的なのはネットワークインタフェースアクセラレータというブロックが設けられている点である。このブロックはX-Gene1でも存在したが、X-Gene2ではRoCEプロトコルをサポートする「HCA(Host Channel Adaptor)」が付いた点が新しい。

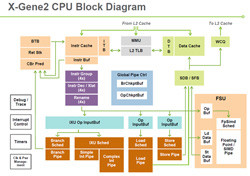

X-Gene2のCPUコアのブロックダイヤの図はX-Gene1と同じであるが、分岐予測関係の資源の倍増、ロードストア命令や分岐命令のスケジューラのエントリ数の増加、データキャッシュのプリフェッチの改善などマイクロアーキテクチャの改善が行われている。

X-Gene2でサポートされたRoCEは、統合型のEthernet上でInfiniBandなどのようにリモートDMAを行うことができるというプロトコルである。従来のEthernetでは、メッセージの送信、受信をCPUが行う必要があり、通信遅延が大きく、バンド幅も制限される場合があったが、RoCEでは、RoCEのアダプタのハードウェアが送信側のノードのメモリから、受信側のノードのメモリへの転送を行ってくれる。その結果、CPUで処理するTCP/IPの場合は50usのレーテンシが、RoCEでは5μsと1/10になる。

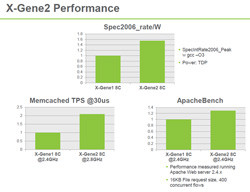

これらの改善の結果、X-Gene2の消費電力あたりのSPECInt_rateの値はX-Gene1に比べて50%あまり高くなっている。ただし、これは性能の向上よりも、消費電力の低減が効いていると思われる。

また、同一クロックで8コアのmemcachedのベンチマークでは、X-Gene1に比べて2倍を上回る性能となっている。これはRoCEによるアクセスレーテンシの改善が効いているのではないかと思われる。そして、WebサーバのApacheBenchでは30%程度の改善となっている。

そして、2015年にサンプル出荷の予定の「X-Gene3(開発コード名:Skylark)」では、ARMコアのマイクロアーキテクチャを改良した第3世代のコアを使い、コア数も最大64コアまで拡張する。半導体プロセスは16nm FinFETプロセスを使い、クロックを3GHzに引き上げる。また、ラック間のインタコネクトという項目が挙げられており、ラック規模のシステムを主要なターゲットにしているX-Gene2と比べて、より大規模なシステムにも対応できるようにすることを意図していると考えられる。

ARMサーバの市場は、まだ、立ち上がったとは言えず、先行きの見通しも意見が分かれれている状況であるが、 Applied Microは、意欲的な製品投入で他社をリードしてシェアを確保する路線を追求している。