Cache

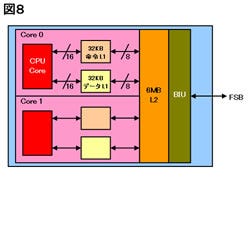

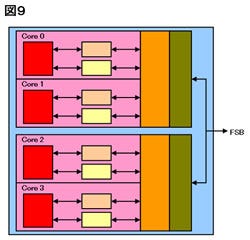

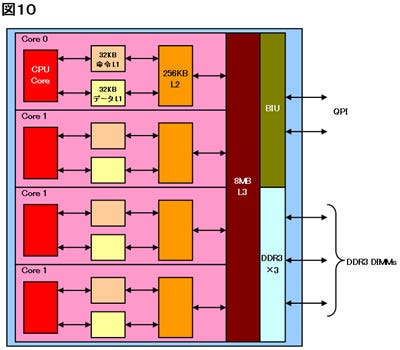

次はキャッシュ性能について確認してみたい。キャッシュの構造は、Core MAから大きく変わったことの一つだ。図8はCore 2 Duo、図9はCore 2 Quad、図10はCore i7の構成である。

CPUコアとL1キャッシュは16Bytes/cycleで、L1キャッシュとL2キャッシュは8Bytes/cycleでそれぞれ接続されており、この16Bytes/cycleというCPUコアとL1間の帯域がCore MAの性能を事実上決めていると考えて良い。この16Bytesはそのまま、ここに出てきたPreDecodeの16Bytes Alignmentに繋がるわけである。

もっとも、これは思うにやはり良いバランスだったのであろう。実際帯域を32Bytes/cycleまで広げたK10は、その代償として猛烈な消費電力の増加を招いており、やっとサーバー向けが出荷開始された45nm SOI世代のShanghaiコアはともかく、65nm SOIのBarcelonaは同じプロセスを使うK8コアに比べ、比較にならないほど消費電力(&発熱)が増加、デスクトップ向けの2.6GHz駆動品であるPhenom 9950はプロセスの小変更(ステッピングは同一なので、内部回路そのものは変更無しと思われる)でやっと今年7月に発売開始しており、しかもTDPは140Wという驚くべき製品になってしまった。このあたりにIntelがどの程度手を付けるか、というのは当然興味ある部分だ。