さて、まずグラフ1~5は、単純な命令(NOP・SUB・XOR・TEST・XOR/ADD)を実行する際のスループットである。

ここでまず、明らかにスループットが異なっていることが判る。NOPは1Byte、SUB~XOR/TESTは何れも2Bytesだから、これを勘案するとL1キャッシュが有効な範囲で、スループットは3.25命令/cycleになっている事が判る。

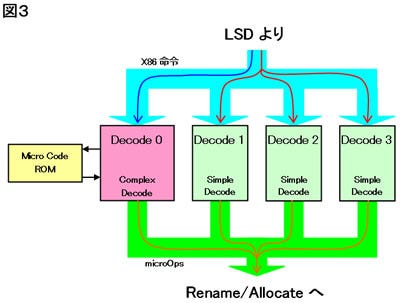

元々、Core MAにしてもNehalem MAにしても、デコードは非対称型である。Core MAの場合4つのデコーダが用意されるが、うち3つ(図3で言うDecoce 1~3)は1cycleでデコードが出来るx86命令のみを取り扱うSimple Decode、残り1つ(Decode 0)は全てのx86命令を取り扱うComplex Decodeとなっている。

ここでComplex Decodeのカバー範囲であるが、どうもSimple Decodeで扱う命令は原則として扱わない事になっているようで、したがってNOPとかSUBといった簡単な命令は図3の赤線の様にDecode 1~3のみで処理されていた模様だ。グラフ1~5でCore 2のスコアの最大値3命令/cycleに一定になっているのは、Decode部の制約か実行ユニットの制約か、がこれまで判断できなかったが、Core i7のお陰でこれがDecode部の制約だと判明したことになる。

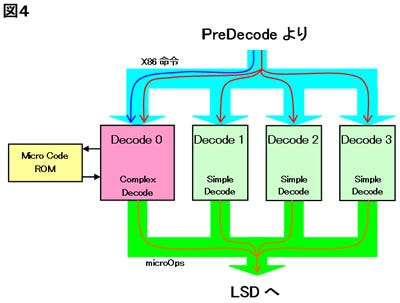

ではNehalem MAは? というと、図4の様になっているようだ。

つまり、これまではSimple Decodeのみで処理していた命令も、Complex Decodeで取り扱えるようになったということだ。ただしSimple Decodeはレイテンシ1、つまり1cycleでDecodeが完了するが、Complex Decodeは内部でMicroCode ROMを参照したりする関係か、Latencyが4cycleほど掛かるようだ。

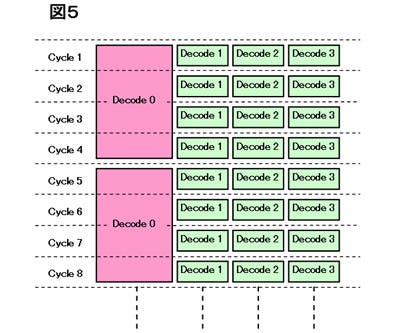

結果として単純な命令は図5の様に、4cycleあたり13命令が処理されることになる。これが3.25命令/cycleという、非常に微妙なスコアになって現れたようだ。