Intelは、45nmプロセスによる低消費電力版SoC技術を開発し、その概要をIEDM 2008で発表した(講演番号27.4)。x86互換の低消費電力プロセッサ「Atom」をベースにしたCPUコアを内蔵するSoCなどに向けたものとみられる。

Intelは2008年に、同社としては初めてのx86互換CPUコア内蔵1チップソリューション(SoC)を相次いで製品化してきた。通信分野向けの「EP80579」(開発コード「Tolapai」)とデジタル家電分野向けの「CE3100」(開発コード名「Canmore」)である。これらのSoCはいずれも、製造に90nmのCMOSプロセスを採用した。次世代のSoCでは65nmプロセスをスキップして45nmプロセスに移行することを同社は表明している。

その45nmプロセスによるSoCの基本技術は、2種類のトランジスタを用意したことにある。1つは2007年のIEDMでIntelが発表した、高誘電率膜/金属ゲート(High-k/Metal gate)技術を基本とするロジック用トランジスタだ。このトランジスタは、電源電圧1.8Vの入出力インタフェース用トランジスタを兼ねる。もう1つは、電源電圧3.3Vと5Vの入出力インタフェースに対応したトランジスタである。ゲート絶縁膜が酸化膜(下層)と高誘電率膜(上層)の2層構造である点が、ロジック用トランジスタと大きく違う。講演では前者をロジックトランジスタ、後者をI/Oトランジスタと呼んでいた。

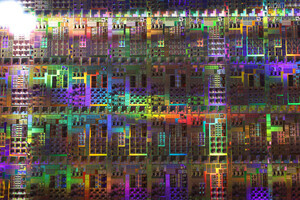

|

|

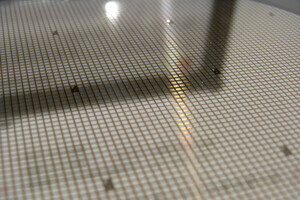

|

45nmのSoCが搭載する2種類のトランジスタ。左が低電圧のロジック用トランジスタ、右が高電圧の入出力回路などに向けたトランジスタ(IEDM 2008の論文集から抜粋) |

試作したトランジスタのゲート部分を電子顕微鏡で観察した像。左がロジックトランジスタ、右がI/Oトランジスタ(IEDM 2008の論文集から抜粋) |

ロジックトランジスタはIEDM 2007で発表した高誘電率膜/金属ゲート技術を基本に消費電力を低減するべく調整をほどこしたもので、ゲート長が40nmと少し長くなっている(IEDM 2007で発表されたトランジスタのゲート長は35nm)。酸化膜換算のゲート絶縁膜厚は1.0nm、リソグラフィ技術は光波長193nmのArFドライ露光、歪みシリコン技術は第3世代版、基板はバルクCMOSであり、これらの要素技術はIEDM 2007と同じである。

試作したロジックトランジスタの駆動能力を示す飽和ドレイン電流(オフ電流1nA/μm、電源電圧1.1V)はnMOSトランジスタが1.08mA/μm、pMOSトランジスタが0.86mA/μmとかなり高い。従来技術であるシリコン酸化窒化膜/多結晶シリコンゲート(SiON/poly-Si)による65nmの低消費電力版プロセスに比べ、nMOSトランジスタのドレイン電流は305向上し、pMOSトランジスタのドレイン電流は87%も高まった。

試作したI/Oトランジスタの駆動能力を示す飽和ドレイン電流(オフ電流0.1nA/μm、電源電圧1.8V)はnMOSトランジスタが0.62mA/μm、pMOSトランジスタが0.52mA/μmである。65nmのシリコン酸化窒化膜/多結晶シリコンゲート技術に比べ、nMOSトランジスタのドレイン電流は17%、pMOSトランジスタのドレイン電流は57%、それぞれ向上したとする。

またゲート長が28nm、ゲート幅が0.9μm、ゲートフィンガ数が100のトランジスタ群(ロジックトランジスタなのかI/Oトランジスタなのかは示されなかったが、ロジックトランジスタと思われる)を試作し、高周波特性を測定した。nMOSトランジスタのトランジション周波数(fT)と最大動作周波数(fMAX)はそれぞれ395GHzと410GHz、pMOSトランジスタのfTとfMAXはそれぞれ300GHzと325GHzである(バイアス条件はドレインソース間電圧1.1V、ゲート電圧0.6V)。いずれも非常に高い周波数であり、バルクCMOSでも高周波回路を十分実現できることを示した。

開発したSoCにはこのほか、高抵抗素子、MIS(Metal Insulator Semiconductor)キャパシタ、MIM(Metal Insulator Metal)キャパシタ、バラクタ、インダクタ、縦型バイポーラトランジスタ、高精度ダイオード、高密度OTP(One Time Programmable)ヒューズを搭載できる。これらの素子によってロジックだけでなく、アナログや高周波などの回路もSoCに集積する。