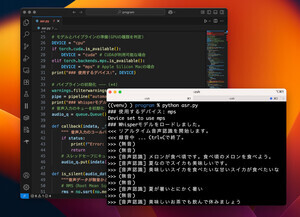

さて、それではPCI-SIG ChairmanであるAl Yanes氏へのインタビューをレポートしたい。

|

|

おなじみAl Yanes氏。彼がChairmanになって結構長い気がする |

─ ではまずGen3について。信号の電圧ですが、Gen1/Gen2と同じですか? それともより低いものになります?

Yanes:Gen1/Gen2と同じ電圧になると思う。

─ 8GHzの信号を通すのは大変では?

Yanes:確かにその通りだ。電圧はそのまま消費電力にも直結する訳だし。ただ我々は電圧レベルを今回変更しないことにした。

─ では配線はどうでしょう? Gen1/Gen2は貫通VIAを使って複数層の配線が可能です。

Yanes:あー、正確なところは知らないが、多分可能だと思う。少なくともデスクトップなどの1 connectorに関しては複数層配線が可能だと思う。知っての通り、Gen2で我々は2種類のEmphasisをサポートしている。これと同じスキームが利用できると思う。

─ IntelのQPIは6.4GHzと、Gen3より低い周波数ですが、にもかかわらず貫通VIAを使った多層配線を禁止していたりしますが、これをどう思われますか?

Yanes:たしかに技術的なチャレンジであることは理解している。ただ先のプレゼンテーション(前のレポートのSuppoerted Topologiesのスライド)にもあるように、我々はすでに貫通VIAを前提にシミュレーションを行っている。

─ ところでPIPE I/Fはどうなると思いますか? もちろんPIPEはIntelの規格ですが、すでにPCI Expressでは広く使われているものです。

Yanes:うーん、多分変更はないのではないかな?

─ 現在のPIPEはGen1だと250MHz/8bit、Gen2だと500MHz/8bitか250MHz/16bitとなってますが、Gen3はどうなるのでしょう?

Yanes:それについては今私からは答えられない。後で調べて返事をするよ。