シリアル・インタフェースの物理層を実現する技術

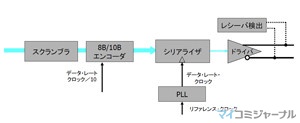

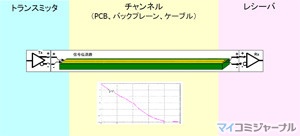

シリアル・インタフェースの物理層は大きく分けて次の3つの要素で構成されます(図4-1)。

- トランスミッタ

- チャンネル

- レシーバ

|

|

図4-1 シリアル・インタフェースの物理層の構成要素。ここでチャンネルの下のグラフはチャンネルの挿入損失を示す。縦軸は減衰量、横軸は周波数で、周波数に依存して増える損失がチャンネルにあることを意味する |

トランスミッタ

差動ドライバ

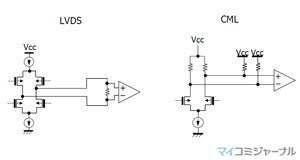

実際の物理層を電気的にドライブする役割を持ち、図4-3のようなLVDS(Low Voltage Differential Signaling)やCML(Current Mode Logic)などの小振幅、差動信号が使われます。これらを総称してLVDSという表現をする場合もありますが、正確にはLVDSはANSI/TIA/EIA-644-Aで標準化された規格のことを言います。

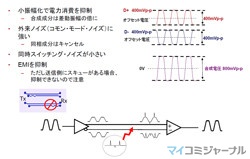

差動伝送のメリットを図4-4にまとめます。

シリアライザ

クロック・タイミングでデータをシリアル化します。例えば2.5Gbpsのインタフェースの場合、250MHz10ビット・データを2.5GHzのクロックで2.5Gbpsにシリアル化します。

8B/10B符号化

シリアル化するにあたって8ビット・データを10ビット・データに8B/10B符号化ルールで符号化します。

符号化の目的はいくつかありますが、

- "0"、"1"の論理状態の継続を最大5ビットとすることで、データ遷移密度を向上させる。換言すれば信号変化が必ず5ビット以内に発生する。この結果、受信のクロック・リカバリを容易化できると共に、DC成分がないため、AC結合や光ファイバでの伝送が可能となる

- データの持つ周波数の広がりが抑制されることにより、伝送路の高周波損失の影響を低減。同ビットの継続は最大5ビット、最小では1ビットなので最長繰り返しパターンは、"0000011111"、最短は"0101010101"となる。例えば2.5Gbpsであれば1ビット長は400psなので、周期は前者4ns、後者800psで、周波数に換算すると前者は250MHz、後者は1.25GHzとなる。つまりデータ・レートの1/10から1/2の範囲に広がりを抑制できる

- シンボル・ロック、周波数偏差吸収、パケット開始/パケット終了などのフレーミング、その他の制御

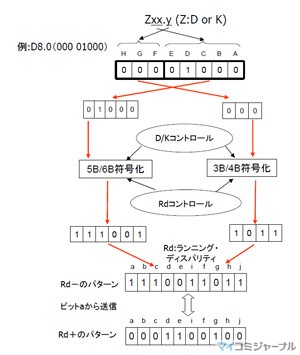

実際の符号化は、図4-5のように8ビットを下位5ビットと上位3ビットに分けて、各々6ビット、4ビットに符号化します。この時に符号列の0と1の数を揃えてDCバランスをとるために、6ビットごと、4ビットごと、あるいは双方に対し極性の反転した2種類のコードを用意し、次にどちらのパターンを送信するかパターン送信中に切り替えます(ラニング・ディスパリティ)。表4-1でflipと記載されている符号は次のコードが反転パターンに切り替わるコードを示します。

なお、同論理状態の継続は基本的に4ビットです。制御コードの一部が他とユニークなコードとして5ビット長を持ち、シンボル・ロックその他で使用されます。シンボル・ロックとは連続して送られてくるビット・ストリ-ムの中から10ビットごとにデータを取り出すことで、規格に応じてK28.1、K28.5、K28.7を基準とし、文字列の区切りとしての意味から"Comma"(略してCOM)と呼ばれます。

8B/10B符号はIBMが1984年に取得した特許(U.S Patent 4,486,739)ですが、権利期間が終了、またシリアル規格のお手本というべきFibre ChannelでもANSI INCITS 230-1994(旧ANSI X3.230-1994、FC-PH:Fibre Channel - Physical and Signaling Interface)として規格化されたため、今日広く利用されています。

参考資料"A DC-Balanced, Partitioned-Block, 8B/10B Transmission Code", IBM Journal of Research and Development, Sept. 1983, Volume: 27 Issue: 5

著者

畑山仁(はたけやま・ひとし)

テクトロニクス社 シニア・テクニカル・エクスパート