パラレル転送方式の限界

パラレル転送方式でデータ帯域幅を拡大しようとした場合、バス幅を広げるか、データ転送速度を上げればよいわけで、従来では、バス幅を拡大するとともに、転送速度を上げてきました。しかしながら、この方法では、

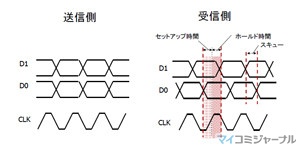

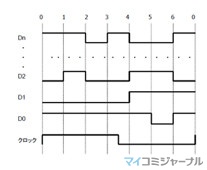

1. 高速化につれて、各信号間のスキューによるタイミングのバラつきが顕著になり、セットアップ/ホールド時間を確保することが困難になります(図3-1)。スキューにはプリント基板のバラつきやデバイスの遅延時間のバラつきが含まれます。

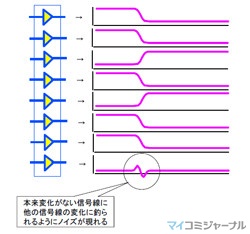

2. 信号の高速化には、1→0、あるいは0→1というロジック変化、すなわち信号変化の高速化が必要であり、各信号間のクロストークや、複数のビットが同時に変化した際に生じる同時スイッチング・ノイズ)などのノイズの増加を招きます(図3-2)。

そこで、ソリューションとして、信号線を削減するために、データをシリアル化し、データ転送速度を大幅に上げる方法を採用したのです。

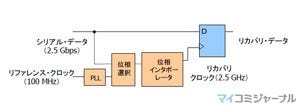

データを受信側で正しく受け取るためにはデータをラッチ(保持)するためのストローブやクロックを必要とします。しかしながらクロックを送るのでは、クロックとデータ間のスキュー問題を解消できません。また周波数的に高いクロックを送信するのは、EMIやクロストークの見地から好ましくありません。そこで送信側ではクロック・タイミングでデータをシリアル化して送信し、受信側ではデータ・ストリームの中からクロックを取り出すという方法、つまりクロックを送信しない方法をとります。

実際は、受信側で生成したクロックを受信データ・ストリ-ムのデータ・レートと位相に合わせます。受信側でこの働きをする機能(回路)のことを、クロック・リカバリ(クロック再生)と呼びます。さらにリカバリされたクロックでデータをラッチする回路を含めて、クロック・データ・リカバリ回路(CDR)とも呼びます(図3-3)。高速シリアル・インタフェースではCDRがキーとなります。

高速シリアル、他にもメリットがいっぱい

高性能を小型パッケージ・低コストで実現

入出力の信号数が増大するとLSIのピン数が増加→パッケージが巨大化→トレース数の増加→プリント基板層数の増加します。これらはすべてコストアップの要因です。

ここでシリアル・インタフェースを採用することで、LSIのピン数の削減→パッケージを小型化→プリント基板層数の削減が可能となり、コストダウンが可能となります。

例えば富士通セミコンダクター(FSL)のUSB3.0-SATAブリッジLSI「MB86C30A」を例にとります。MB86C30Aは7mm角の64ピンLQFP(Low Profile Quad Flat Package)に5Gbps/USB3.0、480Mbps/USB2.0と3Gbps/SATAを各々1ポートずつ実装しています。5Gbps/USB3.0は400MB/s、3Gbps/SATAは240MB/sです。

パラレルのPCIは32ビットで33MHzでしたからデータ帯域幅は133MB/s、しかも64ピンでしたので単純な比較でも同じピン数で4倍以上のデータ帯域幅を達成できています(しかも同じピン数のパッケージではPCIではバスとして1バスしか実装できないことになる)。

細いケーブルで簡単接続・機構設計の自由度が向上

SATA登場以前のパソコンの中を見てみると、マザーボードからFD、HDD、CDの各ドライブ間を接続する何本ものフラット・ケーブルが束ねられて押し込まれています(図3-4)。これらのフラット・ケーブルは筺体内で空気の流れを制限する形となり、筺体設計の制約となります。SATAでは細いケーブルの使用により、空気の流れが向上するため、筺体の小型化や設計の自由度が向上しました(図3-5)。また接続性の高さは、パソコンと外部周辺機器の接続が1本のケーブルで簡単に接続できるUSB2.0を見れば言うまでもありません。

|

|

|

図3-4 昔のパソコン内部。マザー・ボードからFD、HDD、CDの各ドライブ間を接続する何本ものフラット・ケーブルが束ねられて押し込まれている |

図3-5 今日のパソコン内部。マザー・ボードとHDDは細いケーブルだけで接続されている |

なおシリアル・インタフェース自体は特に新しい技術ではありません。ただし、従来では転送レートが低速だったり、ECLなどの特殊なデバイスが必要だったり、伝送メディアが光ファイバだったり、限定的な特殊なコストの高い技術だったと言ってもよいでしょう。しかしながら今日では一般的なFR4基板や銅線を使って伝送でき、前述のようにFPGAでもサポートされるようになったことが広がった大きい理由です。

参考B.クロックに関する他の技術

高速シリアル・インタフェースではクロック埋め込み式以外にも下記のようなクロックを用いている規格もあります。

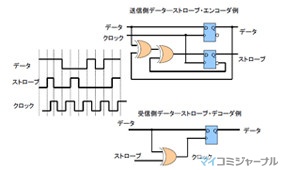

- データ上で同じ論理が2サイクル継続した場合に2サイクル目に論理反転するようなストローブを送信側で生成し、データと並走。1ビットごとにデータとストローブのどちらか一方の信号だけが変化する。受信側でデータとストローブを排他論理和(XOR)することでクロックを作るDS-Link(IEEE1394a、MDDIなど。図B-1)

- データ・レートに対し、1/7や1/10に周波数を落としたサブレートのクロックを並走するインタフェース。ディスプレイ系では多く見られる(FP-Link、DVI、HDMIなど。図B-2)

著者

畑山仁(はたけやま・ひとし)

テクトロニクス社 シニア・テクニカル・エクスパート