10nm未満の世界に突入した半導体の微細加工技術

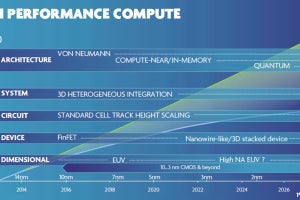

遂に半導体微細加工技術(プロセスルール)はサブ10nmレベルに突入した。相変わらずWebには最先端微細加工技術に関する発表が踊っている。

- Samsungが7nmプロセスによるチップの製造を今年後半に製造開始と発表

- Samsungが独自の3nmプロセスのGAA(Gate All Around) トランジスタ技術によるFETを計画中

- TSMCが7nmプロセスによるApple用次世代CPU、A12の生産開始か?

- Intelの10nmプロセス開発に遅延、2019年にずれ込む見込み。

- GMOが独自開発のマイニングチップを7nmプロセスで製造

NAND型フラッシュメモリの世界では回路設計はすでに立体構造になっているので従来からの何nmプロセスというだけではその先端性は表現できず、64層とか96層などという表現になっているらしい。ここに並べた発表は主に最先端ロジック半導体の話である。それにしても10nm以下の線幅のプロセスルールが現実化するだろうなどとは「ムーアの法則」で知られるかつてIntelで活躍したゴードン・ムーアでさえ想像していなかったのではないだろうか?

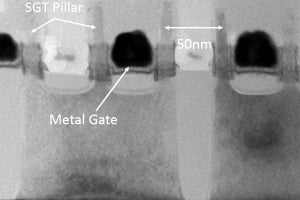

私はAMDがまだ自社ファブを持っていた時、最後のファブとなったドレスデン(現在はGlobalfoundriesのファブ)のプロセス技術研究所でまだ基礎研究段階のプロセス技術の電子顕微鏡写真を直に見た覚えがある。うろ覚えではあるが、その写真には縦に走る柱のようなものの中身に球体の粒が連なっていた。これは何かと尋ねると、ドイツ人の実直そうな研究員は微かに笑いながら、「それは分子の粒だよ、このまま開発が続けば将来のプロセス技術は分子の直径が何個分かというオングストロームのレベルになるね、まだずっと先の話だけどね」、と答えたのをはっきり覚えている。1オングストロームは0.1nmであるから10nmから先のプロセスルールは分子の世界に入ってゆくという、気の遠くなるような話である。

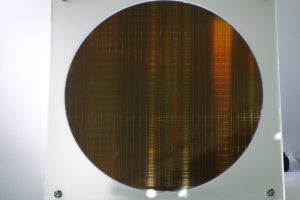

プロセスルールは微細であるに越したことはない。それは動作周波数などの製品の性能に大きく関係するし、ダイサイズなどの製品コストにもダイレクトに関係する半導体メーカーにとって最も重要な要件である。しかし微細加工技術の研究開発にはべらぼうなコストがかかる。しかも自社でファブを運営するということはその研究開発コストと、それ以上にべらぼうにかかるファブの建設コストを自前で抱えることになる。

その総費用は私が現役の時代はファブ当たり3~4000億円くらいであったが、現在では1兆円超の巨額投資が必要とされる。こういった事情で、今となっては半導体企業で最先端微細加工技術とそれを移植する自社ファブに果敢に投資するのはIntelやSamsungなど限られた数の大手のみになってしまい、多くは自社ファブを持たないファブレスのブランドとなった。そういった意味では、プロセスルールの数字を自社の実力として華やかに宣伝するのは主にファウンドリ会社である。しかし最近気になるのは、ファブレス・ブランドがナノメーターの数字をマーケティング的な使い方でアピールする点である。次の点が私の気になる点である。

- プロセスルールはあくまで製造技術の指標である

- プロセスルールは製品デザインの構造、トランジスタ数、ダイサイズなど他の変数と関係づけて議論されるものであって、それ自体は最終製品の性能の表示とはならない

- 言い換えればエンドユーザーに提供される価値の指標はそのデバイスの性能、価格、品質であり、プロセスルールの数字自体は製品がエンドユーザーに提供する価値の尺度ではない

- ファブレスのブランドは実際の製造はTSMCなどのファウンドリに任せなければならないので、所望のプロセスのラインで、どのタイミングでどれだけ生産できるのか(ウェハの投入はどれだけか)という決定権は基本的にファウンドリ側にある。

Intelのプロセス技術を常に一世代遅れで追いかけたAMDの必殺技「SOI」

私がここまでプロセスルールに拘るのはAMDでの経験があるからである。プロセスルールの微細化に関しては次の要件がある。

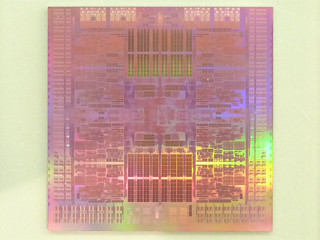

- 微細であればあるほど同じデザインではダイサイズは小さくなり、一枚のウェハからとれるデバイスは多くなるのでコストは下がり、エンド価格では俄然有利となる

- その微細加工をより高集積の次世代製品の製造に使うこともできる。同じ世代のマイクロプロセッサでも、より大きなキャッシュメモリ(SRAMでできている)を集積することができるし、トランジスタ数がさらに多い新たなデザインの製造には最先端のプロセスが必須である

- 一般的に言えば、微細加工技術が進めばデバイスの動作周波数は上がり、高性能のデバイスを製造できる(しかしその場合には周波数の上昇に伴う発熱の問題に対処する必要がある)

前述したように最先端プロセスの開発とそれを移植したファブの稼働にはべらぼうなコストがかかるので、AMDは10倍以上の事業規模であるIntelと戦う時には常に不利な立場にあった。

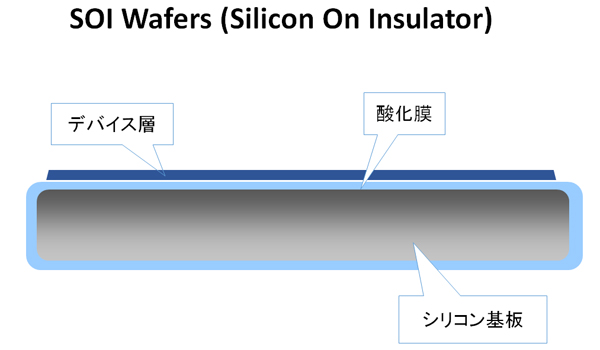

K6、K7、K8と製品のデザインの先進性ではIntelに先行したが、それを製造する自前のプロセスは常に一世代遅れていた。Intelは常に業界で最先端のプロセス技術を開発し、量産ラインに移植していたが、研究開発投資に限界があるAMDは常に一世代後で追いかけるのが精いっぱいであった。そこでAMDは大きな賭けに出た。SOI(Silicon On Insulator)ウェハを使用することである。通常の半導体は高純度のシリコンウェハを微細に研磨したバルクウェハを使う。Intelもそうであった。しかし半導体ウェハにはいろいろな種類がある。その中でAMDはシリコンの表面に酸化膜を施したSOIウェハを使用するという賭けに出た。SOIウェハには次の特徴がある。

- 一般的にSOIウェハを使用するとCMOSロジックの動作周波数を高くすることができる

- SOIはシリコンの周りに酸化膜を形成しており、デバイスを作りこんだデバイス層の下側に酸化膜がある構造なのでリーク電流を抑えられる(消費電力を抑えることができる)

- その分、回路の作りこみはより困難になる。ウェハの価格もバルクよりはるかに高い。

微細加工技術ではIntelより一世代遅れていたAMDであったが、SOIウェハの使用でそのハンディキャップを見事に乗り越えた。初代K7(Athlon)のプロセスルールは0.25μmであったが、ライバルのIntelのPentium IIはすでに0.18μmで製造され、動作周波数で常にリードしていた。このハンディキャップを乗り越えるために、AMDはK7の15段(浮動小数点演算部分も含む)という深いパイプライン・アーキテクチャを考案し、Intelのバルクウェハに対しSOIウェハを使用した。SOIウェハの使用についてはその技術的困難さから当時業界では疑問視する声が高かったが、AMDは敢えてそのリスクを冒してプロセスルールのハンディを克服したのだ。半導体デバイスの優位性はプロセスルールだけでは決まらないのである。

著者プロフィール

吉川明日論(よしかわあすろん)1956年生まれ。いくつかの仕事を経た後、1986年AMD(Advanced Micro Devices)日本支社入社。マーケティング、営業の仕事を経験。AMDでの経験は24年。その後も半導体業界で勤務したが、今年(2016年)還暦を迎え引退。現在はある大学に学士入学、人文科学の勉強にいそしむ。

・連載「巨人Intelに挑め!」を含む吉川明日論の記事一覧へ