HPEの光モジュール

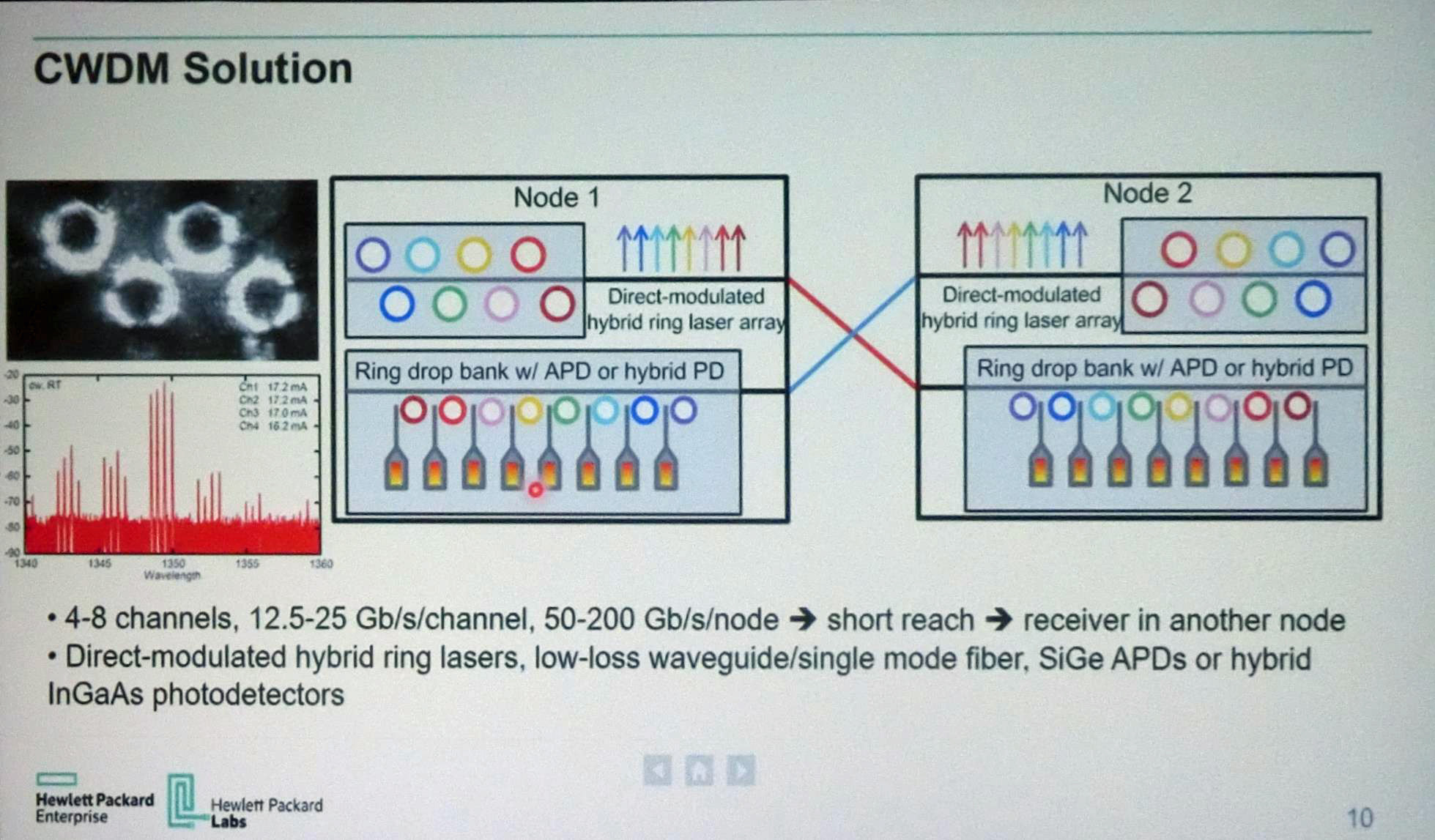

HPEのAshkan Seyedi氏は、同社のCWDM(Coarse Wavelength Division Multiplexing)光モジュール技術がポストムーア時代の情報処理で重要になると述べた。

数10nmと波長間隔が長いCWDMは、比較的安価に実現でき、それでも複数の波長の光を1本の光ファイバで伝送でき、高いバンド幅を持つ。

次の図はプリント基板にマウントできる4波長のCWDMモジュールを示す。

HPEはメモリセントリックなデータ処理を行う「The Machine」を開発している。そして、中心となるメモリと多数のプロセサを接続する高帯域、低レーテンシの「Gen-Z」というインタコネクトを、コンソーシアムを作って推進している。このGen-ZにCWDM光チャネルを使えば、コンパクトに高帯域、低レーテンシのインタコネクタが作れる。

次の図はGen-Z規格のインタコネクトを使うThe Machineの光インタコネクト部分の写真である。

光の変調には、マッハツェンダー変調器が良く用いられるが、サイズが大きいのが欠点である。これに対して近接して配置されたマイクロリングの共振周波数を変えて、吸収量を変化させる変調器を提案している。この変調器は、次の図のように人間の髪の毛の断面積に収まるコンパクトさで実現できるという。

そして、HPEはCMOSチップとシリコンフォトニクスのコンポーネントを混載するインタポーザの開発を行っているという。CWDMを使えば波長の数を増やすことも容易で、波長ごとのルーティングで適応的にバンド幅をアサインすることも可能である。

また、DWDM(Dense Wavelength Division Multiplexing)技術を使い1本のファイバで50波長以上を多重化することも可能である。チャネル当たり20Gbit/sとすると、1本のファイバで1Tbit/s以上の帯域が得られ、数10kmの伝送ができる。

CWDMでは4-8チャネルで12.5-25Gbit/s/チャネルの伝送。伝送距離も短いが、安価であるのが特徴である。

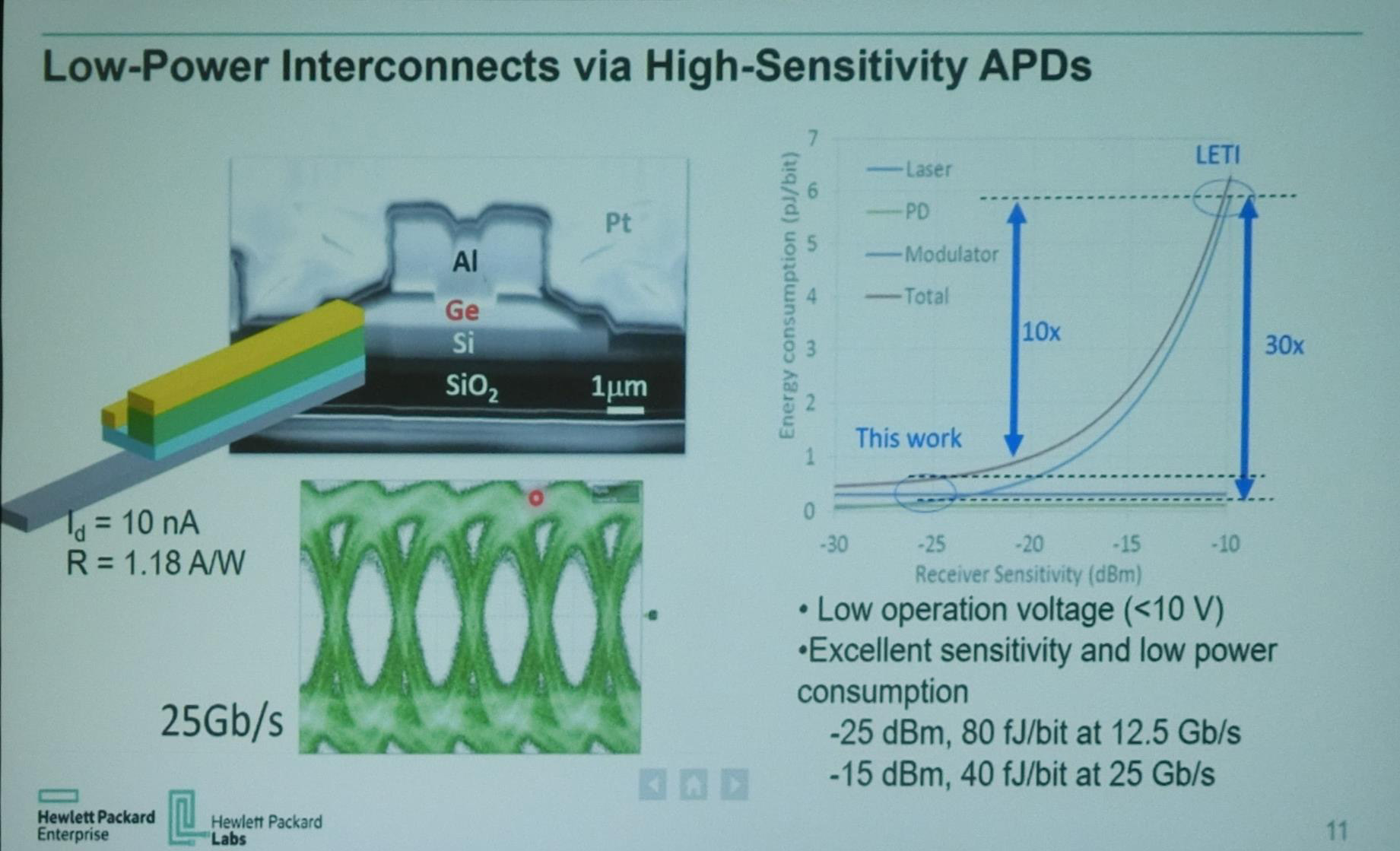

そして、HPEは低電力で伝送ができるインタコネクトも開発した。変調器は10V以下という低電圧で動作し、低電力で高い感度を持つ受信機を開発した。その結果、ビット当たりの消費エネルギーは1/10となった。

HPEの光技術を使えば、1本のファイバの接続で済み、ビット当たりの消費電力を少なくできる。そして、20km以上の伝送もできる。インタポーザによる実装は、高密度で消費電力を減らし、チップの周辺に入出力を集中させる必要がなく、チップのフロアプランも容易になる。 リンクのバンド幅は、波長の多重化を増やせば拡大することができ、将来のバンド幅要求にも応えられるというメリットもある。

-

1本の光ファイバの接続で済み、低電力で長距離の伝送ができる。波長を増やせば、帯域の拡張ができ、将来のバンド幅要求にも応えられる。インタポーザを使えば、消費電力を減らし,チップのフロアプランも容易になる

MITの3次元実装技術

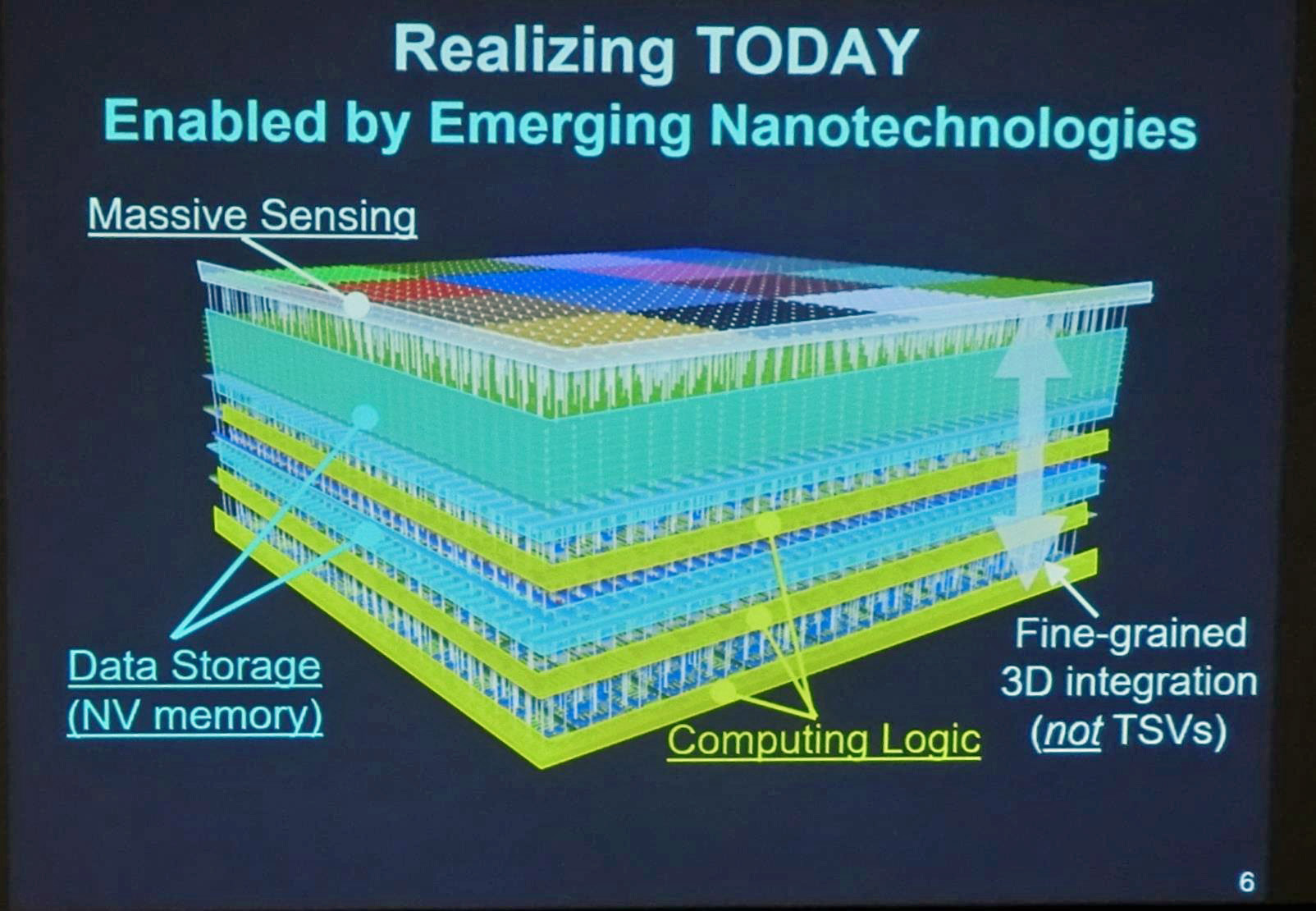

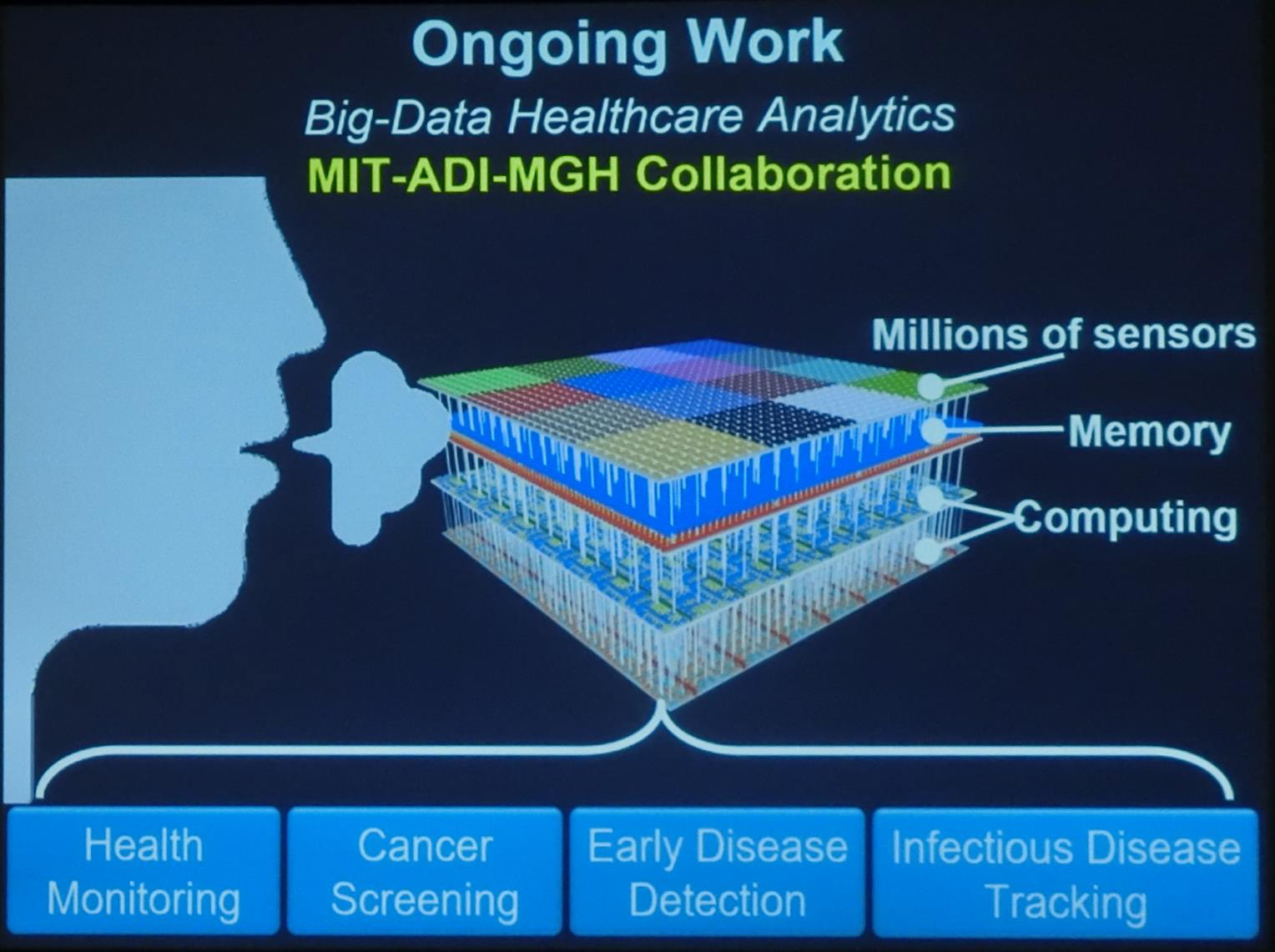

MITのMax Shulaker氏は超高密度の3次元実装がポストムーア時代を乗り切る鍵であるという。現在、開発しているものは、最上層に大量のセンサを搭載したチップを置き、不揮発性メモリのチップやロジックチップをTSVより高密度のチップ間接続で3D化するものであるという。

-

最上層には大量のセンサを搭載するチップ、下層には不揮発性のストレージチップとロジックチップを積層し、TSVよりも高密度のチップ間接続を使って3D積層を行う (ここからの図は、MITのMax Shulaker氏の発表スライドを撮影したものである)

TSVのようにチップ上の配線に比べると巨大な接続ではなく、ナノスケールのインターレイヤビア(ILV)でチップ間を接続する。

ロジックはカーボンナノチューブを使ったトランジスタを使い、メモリはレジスティブRAMを使う。どちらも200℃以下の低温プロセスで作れる。

これらの新しいデバイスを組み合わせると、メモリとロジックが隣接し、超高バンド幅で接続されているので、新しいアーキテクチャが自然に実現できる。

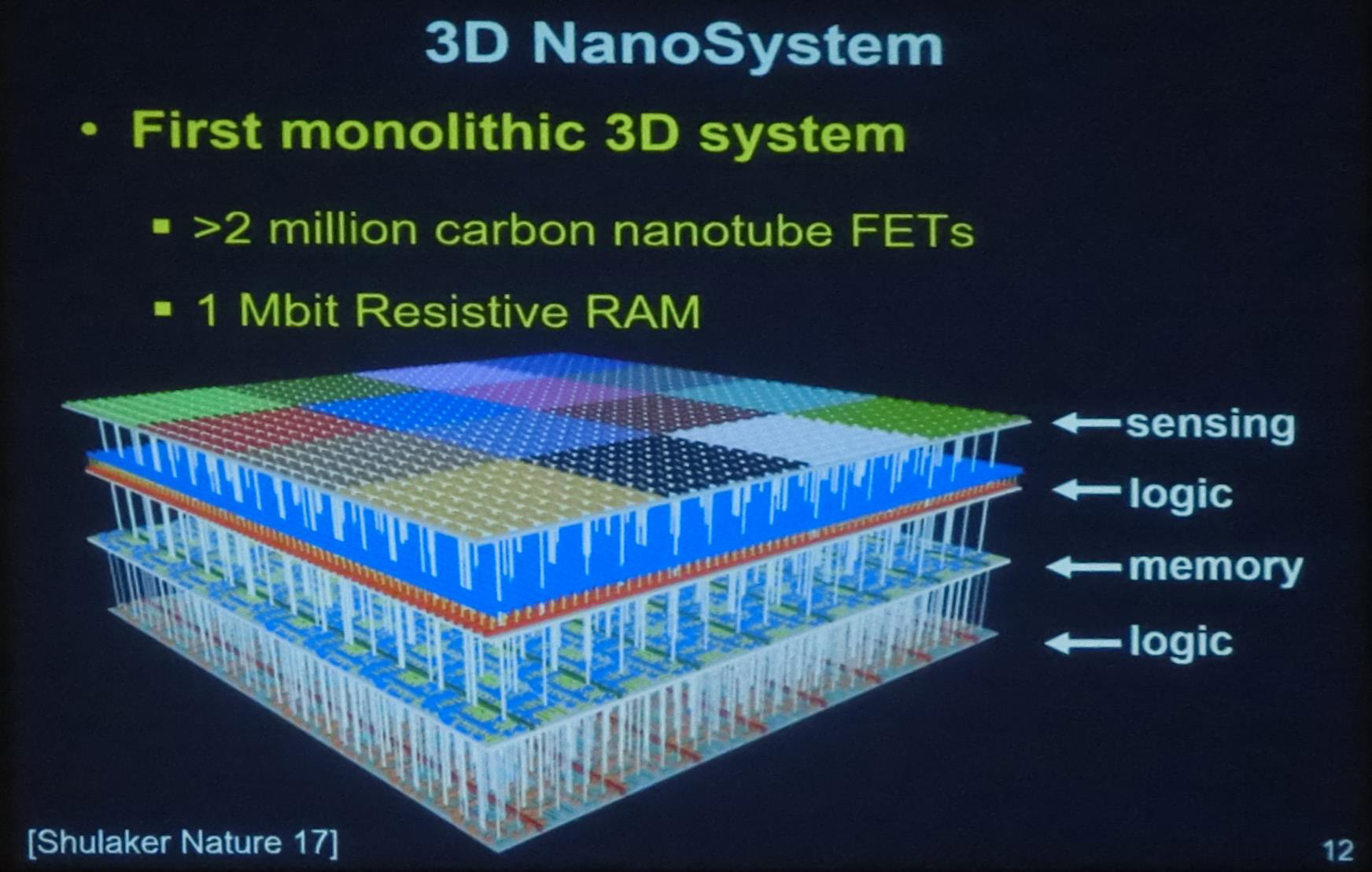

Shulaker氏は、200万個以上のカーボンナノチューブを搭載したチップと1MbitのレジスティブRAMを集積したチップを作り、これらを積層したプロトタイプ積層モジュールを作って、Nature誌に発表している。なお、Shulaker氏は、元々はスタンフォード大学のSubhasish Mitra教授の研究室に所属していた人で、このNatureの論文もMitra教授らとの共著となっている。

-

Shulaker氏らは、センサとロジック、メモリ、ロジックを積層した4チップの3Dモジュールを作りNature誌に発表した。ロジックチップは2M個以上のカーボンナノチューブトランジスタを集積し、メモリチップは1MbitのレジスティブRAMを集積している

このプロトタイプチップは、ガスを検出し、そのデータをレジスティブRAMに格納し、ロジックチップで分析を行って結果を出力するもので、健康管理やがんや他の病気の早期検出、伝染病の追跡などに使える。

-

このプロトタイプチップは、ガスを検出し、そのデータをレジスティブRAMに格納し、ロジックチップで分析を行って結果を出力する。健康管理への応用を目指している。このプロトタイプチップは、ガスを検出し、そのデータをレジスティブRAMに格納し、ロジックチップで分析を行って結果を出力する

この応用はスーパーコンピューティングとは言えないかも知れないが、このような積層モジュールが作れるようになれば、スーパーコンピューティングでも有効に利用できることは明らかである。

(次回は1月17日に掲載します)