前回の記事「Spectre/Meltdownを防ぎ、安全な投機実行を可能にするSafeSpecの考え方」はコチラ

SafeSpecの性能に与える影響

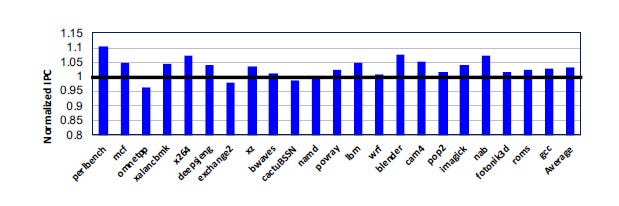

プロセサ各社がSpectreやMeltdown対策で出しているパッチの多くは、性能を低下させる。次の図は、SafeSpecを適用する前のプロセサの性能を1.0と正規化したSafeSpecを加えた場合の性能を比較したものである 。

ベンチマークプログラムによってばらつきがあるが、SafeSpecの相対性能は0.96~1.1倍となっており、右端の幾何平均では3%程度高い性能になっている。

SafeSpecの相対性能が上がっているのは、シャドウ構造が付け加えられることにより、キャッシュやTLBの有効なエントリ数が増えていることが効いていると考えられる。また、投機状態はシャドウ構造に格納され、本来のキャッシュやTLBの内容は投機情報で乱されないので、ミス率が減少する効果もあると思われる。

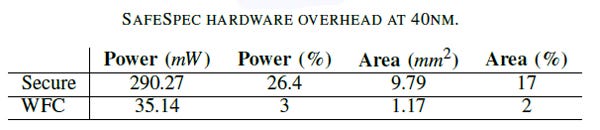

次の表は、SafeSpecを実装するためのオーバヘッドをまとめたものである。Secureと書かれた行は、シャドウエントリの数を理論的な最大の投機実行があっても耐えられる数とした場合で、WFCと書かれた行は99.99%の場合は足りる数とした場合である。使用半導体プロセスとして40nmを想定した場合、Secureの消費電力オーバヘッドは290.27mWで、これは26.4%の増加にあたる。チップ面積のオーバヘッドは9.79mm2で、17%の面積増加に当たる。

WFCの場合は、0.01%のケースではシャドウ構造を介したリークが発生しうるが、チップ面積、消費電力ともにSecureの場合の1/8程度のオーバヘッドで済む。

今後の研究課題

この研究では、i-cache、d-cache、そしてiTLB、dTLB経由の秘密情報のリークを検討し、これまで知られていなかったi-cacheを使う攻撃が可能であることをProof-of-Conceptコードを作って示した。

しかし、この研究では、1個のプロセサコアでは1つのスレッドを実行するという状態しか想定していない。IntelのCoreやXeonプロセサは1個のコアを2つのスレッドで共用する実行を行っており、スレッド間の情報リークが起こるかもしれない。

また、シングルスレッド実行でも、分岐予測機構、DRAMバッファ、メモリプリフェッチなど予測的に実行を行う機構があり、これらの構造も攻撃を受けるメカニズムがあるかも知れない。

今後、これらの構造のセキュアな実現を研究していくつもりであるという。

このような体系的な研究は、今回の論文で始まったもので、SafeSpecの観点から見れば、リーク攻撃を受けるおそれのある部分が、まだまだ、出てくる可能性がある。これらのすべての穴をふさぐとなると、プロセサハードウェアの設計の考え方に大きな影響が出てくる可能性もある。

しかし、セキュリティの重要性は増すことはあっても減ることは無いので、この分野の研究に力をいれることは重要であると考えられる。