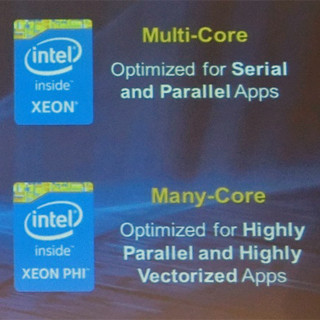

IntelのBorkar氏はエクサノードではシステム効率とコストが重要と指摘。

続いて、IntelのExtreme-Scale Technologyの開発を担当するShekhar Borkar氏が、「HPC Node Architecture - What it is、& What it should be…」と題して発表を行った。

Borkar氏は、HPCにおける6つのトップ挑戦項目として、システムの電力とエネルギー、新規な効率の高いメモリサブシステム、究極の並列処理、新しい実行モデル、抗堪性(故障回復力)、システムの効率とコストを上げた。これらの中でも、最後のシステムの効率とコストが重要であるという。

エクサ時代のハードウェアとソフトウェアの設計アプローチ

これらを踏まえた将来のハードウェアの設計アプローチとして重要なことは、

- 0.4V程度まで電源電圧を下げるNTV(Near Threshold Voltage)ロジックと消費エネルギーを低減するメモリ設計

- NTV化で影響が大きくなるバラつきを吸収する設計

- 細かい単位での電源管理

- 反省材料を提供する消費エネルギーや性能の測定機構の組み込み

- 階層的なヘテロなチップ構成

- メモリサブシステムの徹底した見直し

を挙げた。

将来のソフトウェアのアプローチとしては、以下の6項目を挙げた。

- 10億レベルの並列度を扱えるプログラムモデル、データ局所性の実現

- データフローの考え方で少ない努力で高性能を実現するプログラムモデルやシステム

- 新しい実行モデル。イベントドリブンで非同期にダイナミックにスケジュールを行うランタイムシステム

- 気付きや反省をもたらすモニタ類

- 挑戦的なアプリで、新しいアルゴリズムの開発を促す。局所性の実現が容易で、コアからメモリに向かって減少して行くバンド幅にも耐えられるプログラム

- システムレベルの抗堪性

微細化の貢献は縮小し、並列化を更に増やすことが必要

歴史的にGigaからTeraへの性能向上は、ムーアの法則の微細化による性能向上が32倍、そしてコア数が32倍という感じで1000倍の性能向上を実現した。そして、TeraからPetaの性能向上では、微細化の貢献は8倍に止まり、コア数の増大による並列度の向上が128倍であった。しかし、PetaからExaの1000倍では、微細化は1.5倍程度の貢献しかできず、並列度の向上で670倍の性能向上を実現しなくてはならないという。

|

|

図4.14 GigaからTera、そしてPetaとトランジスタの性能向上の貢献は減少。Exaに向けてはトランジスタの性能向上に期待できるのは1.5倍で、残りの670倍は並列度の向上で稼がなければならない |

マイクロアーキテクチャと消費エネルギー

プロセサは、オンチップのキャッシュ、スーパースカラ、Out-of-Orderと投機実行、深いパイプライン化とそれを元に戻すパイプライン段数の低減というアーキテクチャ的な改善が行われてきた。図4.15はこれらの改善がチップ面積、整数演算性能、浮動小数点演算性能、そしてエネルギー効率に与えた影響をグラフで表したものである。例えば、オンチップのキュッシュはチップ面積を4倍あまり大きくし、整数演算性能を2.3倍程度に向上させ、エネルギー効率的には若干改善をもたらしている。

スーパスカラ、O-o-Oと投機実行、深いパイプラインなどはチップ面積を増大させているが、それなりに整数や浮動小数点演算を向上させている。しかし、それぞれのマイクロアーキテクチャはエネルギー効率的には20~30%の効率低下を引き起こしている。増加させたパイプライン段数を元に戻すという変更は整数演算性能を10%程度、浮動小数点演算性能を40%近く低下させているがエネルギー効率を3.5倍に向上させている。

速度重視の時代には、クロック周波数を上げるためにパイプライン段数を深くしたが、消費電力が問題になり始めると、深いパイプラインが姿を消したのはこのためである。